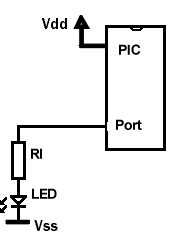

I Port come uscita digitale : che resistenza

per il LED ?

|

Queste pagine nascono dalla

necessità di chiarire un problema marginale, ma non per questo inutile.

Da parte di un (troppo) gran

numero di autori, e non solo quelli presenti sul WEB, ma anche in

pubblicazioni e libri, la gestione di un pin in uscita è

considerata in modo molto superficiale e approssimativo.

Ad esempio, si arriva a scrivere

che:

- dal

foglio dati (Absolute maximum rating) la corrente che il PIC può erogare

(source) o assorbire (sink) su ogni pin in è 25 mA massimi.

Quindi se devo pilotare un carico, ad esempio un LED, basta che non ecceda

questo limite, introducendo una resistenza in serie.

|

Se la Vdd è 5 V e la corrente che si vuole fare

passare nel LED è 10 mA, allora per calcolare Rl basta fare :

Rl = Vdd /

Iled = 5 /

0.01 = 500 ohm

1.0 |

Proprio così !

Questo calcolo non è semplice, ma semplicistico, con ben poca conoscenza di elettronica, in quanto,

come minimo, manca di considerare che il LED

ha una

sua caduta di tensione Vled, per niente

trascurabile a così basse tensioni e che dipende dal tipo di LED. Questo deve

essere valutato.

Supponendo la caduta dio tensione del LED Vled = 1.7

V, un calcolo più ragionevole sarà :

Rl = (Vdd - Vled)

/ Iled = (5 - 1.7) / 0.01 = 330 ohm

1.1

il che è ben diverso dal primo risultato.

Se avessimo usato una resistenza da 500 ohm, la corrente sarebbe stata :

Iled = (Vdd - dVled) / Rl = (5 - 1.7) / 500 = 6

mA

1.2

e non 10 mA (- 40%) !

Certamente il LED si accende lo stesso anche con 6 mA perchè gran parte di

questi dispostivi di uso comune si illumina anche con correnti molto inferiori

a quella nominale e l'

occhio non sempre è in grado di percepire una grossa differenza.

Però se si trattasse di qualche altro dispositivo, dove la corrente minima è

un parametro più legante, ad esempio un relè o un opto isolatore, ecco che le cose potrebbero

andare meno lisce.

Quindi, prima di prendere per buona ogni cosa che arriva dal WEB, è

opportuno verificarla non in base alla sua brillantezza, ma alla sua

correttezza.

Però, chi si desse la pena di misurare la corrente , troverebbe che il

valore risulta minore dei 6 mA calcolati.

Un noto autore, in un suo libro, nota casualmente questo e conclude che il valore calcolato

delle correnti e quello misurato sono "abbastanza simili" !

Il problema è che, nella tecnica e ancor più nella scienza, pur consci

della presenza inevitabile di errori di misura e delle inevitabili tolleranze

dei materiali, un "abbastanza simile" non è per niente un risultato

accettabile senza motivazioni valide.

Se è come previsto, il modello di partenza è corretto; se

non è come previsto, è probabile che il modello sia errato.

Ed è questo il caso.

Infatti, se consideriamo che i PIC sono dispositivi in tecnologia MOS, è

evidente che tutte le componenti interne sono realizzate con elementi MOS,

compresi i driver di uscita.

E una tipica uscita a transistor in grado di fornire (source) corrente o

assorbirla (sink ) è un totem pole, realizzato con un MOS P a fare da

interruttore verso la Vdd e un MOS N verso la Vss.

Ed è proprio questo che risulta dagli schemi di principio forniti dal

costruttore.

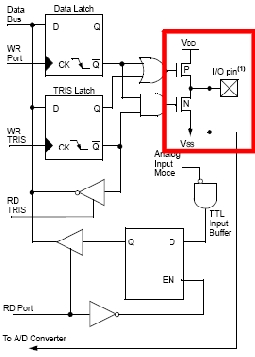

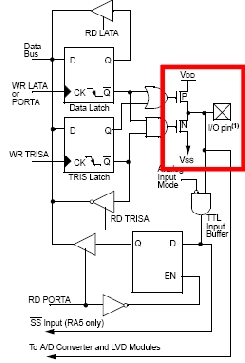

| Mid-range |

Enhanced |

|

|

La tabella schematizza, ad esempio, la struttura dei PORTA, ma ogni

altro port è lo stesso: potrà mancare la funzione analogica, ma il sistema

del totem pole è uguale per tutti.

|

|

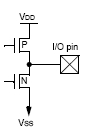

La struttura totem pole prevede due MOS complementari, uno P verso

la Vdd e uno N verso la Vss.

Questo è tipico delle tecnologie a MOS complementari (CMOS). Quando i

MOS sono disabilitati, l' impedenza di uscita è virtualmente

infinita.

Quando uno dei due viene attivato, la sua resistenza cade a valori

inferiori ai 200 ohm:.

Il MOS N collega il pin di IO alla Vss e il MOS P lo collega alla Vdd.

La logica di comando evita che i due MOS siano attivati

contemporaneamente. |

|

Ricordarsi che nei PIC fa eccezione il port

RA4, che ha una uscita open

drain: in questo caso è presente solo il MOS N e per attivare un carico in

uscita sarà possibile collegarlo solamente tra il pin e la Vdd. |

Inoltre non hanno struttura totem pole i pin che possono essere impiegati

solamente come ingressi, ad esempio MCLR/RE4.

Nel totem pole ( e anche nel MOS N dell' open drain), trattandosi di switch MOS, essi presenteranno, al passaggio della corrente,

una certa caduta di tensione dipendente dalla loro resistenza interna.

Ed in effetti , quando ci si riferisce a MOS e non di transistor a giunzione,

è più corretto parlare di resistenza più che di caduta di tensione :

un transistor o un diodo ha una tensione di conduzione tipica che resta

ragionevolmente costante al variare della corrente che l' attraversa, mentre

un dispositivo MOS presenta una resistenza, altrettanto ragionevolmente

costante per il range di impiego previsto. Una ulteriore considerazione

immediata è quella che, per ragioni di tecnologia costruttiva, la resistenza

interna degli elementi P è generalmente più alta di quella degli elementi N.

La conseguenza è che, a pari corrente, la caduta di tensione introdotta sarà

maggiore per un carico pilotato verso la Vss (attraverso il MOS

P)

piuttosto che dalla Vdd (attraverso il MOS N). Ed infatti la conferma è nei

parametri D090 e D080 del foglio dati, dove vengono fornite le seguenti

indicazioni :

| Param. no. |

Symbol |

Characteristic |

Min. |

Max. |

Conditions |

| D080 |

Vol |

Output low voltage |

- |

0.6 V |

Iol = 8.5 mA Vdd = 4.5 V |

| D090 |

Voh |

Output high voltage |

Vdd-0.7 |

- |

Ioh = -3 mA Vdd = 4.5 V |

Ovvero, ci potranno essere nelle peggiori condizioni, una caduta di tensione

di 0.6 V sul MOS N e

0.7

V sul MOS P. Supponendo di alimentare il LED tra il pin di I/O e la

massa (Vss), la corrente che scorre nel LED non è determinata

solo la caduta di tensione della resistenza dVR

e da quella del LED dVled

, ma anche da quella sul MOS P del drive dVP.

Questo porta a modificare il calcolo fatto in precedenza in : R

= [(Vdd - dVP) - dVled] / Iled = (5 - 0.7 - 1.7 ) / 0.01 = 260 ohm

1.3 E dovremmo essere già ad un buon punto, che, se si

osserva, è ben diverso dal primo approccio semplicistico : la R è

diventata circa il 50% del valore prima "calcolato" !! E

nel caso del drive dalla Vdd, attraverso il MOS N :

R

= [(Vdd - dVN) - dVled] / Iled = (5 - 0.6 - 1.7 ) / 0.01 = 270 ohm

1.4 Come era sensato aspettarsi non c'è una grossa differenza

tra i due drive, la cui caduta di tensione si differenzia di solo 0.1 V.

E'

capitato, però, di leggere una semplice considerazione estrapolata dai dati forniti

da Microchip sul questa caduta di tensione nei MOS :

-

se la caduta di tensione è 0.6 V @ 8.5 mA , la resistenza

equivalente dell' interruttore N è di circa 70 ohm

-

se la caduta è 0.7 V a 3 mA, la resistenza equivalente

dell' interruttore P è di circa 233 ohm

Per i dati forniti dal costruttore, questo è perfettamente

corretto, ma è in contraddizione con l' Absolute maximum rating dove si

dichiara una corrente massima di 25 mA.

Infatti se la resistenza del MOS P fosse 233 ohm, il pin non avrebbe alcuna

possibilità di erogare 25 mA alla tensione nominale di 5 V, neanche in corto

circuito diretto sulla Vss, perchè : I

= V / R = 5 / 233 = 21 mA

1.5 mentre è semplice verificare con una esperienza che, caricando il pin

con una resistenza da 100 ohm o meno, la corrente di 25 mA viene superata con

facilità (e mettendo in corto il pin a massa per un adeguato tempo, lo si

manda fuori uso !). Dunque questo vuol dire che le resistenze indicate da Microchip

sono parametri estremi, di gran sicurezza, mentre l' esperienza indica che i

MOS integrati hanno resistenze molto minori.

Ne è nata la curiosità di

verificare quale sia la resistenza di conduzione del componente reale.

Quindi sono state effettuate misure caricando un pin con una cassetta di

resistenze di precisione e misurando la corrente.

Sono state provate correnti tra 0.5 e 30

mA, sia per sink current che per source current.

Per ogni valore di resistenza, e quindi di corrente, è stata misurata la

caduta di tensione sul drive, misurando la tensione tra pin e massa per il

drive N e tra pin e Vdd per il drive P. L'

esperienza, per ragioni di tempo, non è stata estesa a molti chip, ma sono

stati provati alcuni elementi della famiglia PIC18F23xx, 43xx, 25xx e 45xx,

ottenendo risultati molto simili.

- Per una variazione della corrente di carico da 0.5 a 20 mA, nel caso di

drive dalla Vdd (MOS P) la resistenza riscontrata è circa 56-60 ohm

- Per una variazione di carico da 0.5 a 22 mA la resistenza del MOS N è

circa 19-22 ohm

quindi valori molto migliori di quelli del foglio dati, ma comunque

confermanti la maggiore resistenza dell' elemento P.

Certamente i valori di resistenza di questi MOS integrati sono enormemente

più alti di quelli di dispostivi discreti, dove la resistenza scende , per

elementi di potenza , anche a millesimi di ohm, ma, evidentemente, è il

massimo possibile per la tecnologia di costruzione di un processore embedded

(questi dati infatti sono simili a quelli dichiarati da altri costruttori).

Inoltre, durante i test, le resistenze con correnti elevate

(oltre i 22 mA) crescevano in modo sensibile e anche questo rientra

pienamente nelle caratteristiche di un MOS, la cui resistenza di conduzione (Ron)

varia sia con la temperatura, ma anche con la corrente

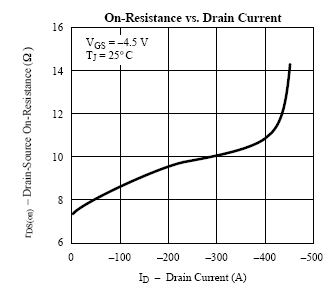

|

Questa è la curva corrente di Drain-Ron per uno Temic VP2410L,

piccolo MOSFET a canale P in contenitore TO92.

E' ben visibile l' aumento brusco della resistenza di conduzione

oltre un certo livello di corrente di drain |

Ed in effetti, la resistenza interna degli interruttori MOS , durante i

test, era circa costante fino alla soglia di una ventina di

milliampere, dove saliva decisamente. Nelle prove fatte :

- la resistenza del canale P che a 8,5 mA era circa 57 ohm, a 20 mA era

salita a circa 64 ohm, mentre a 27 mA saliva oltre i 75 ohm (+30%)

- la resistenza del canale N , che a 8.5 mA era circa 20 ohm, saliva

intorno ai 22 ohm (+ 10%) per correnti oltre i i 25 mA

Dunque , nei dispositivi provati, restando nell' ambito di correnti al di

sotto dell' Absolute maximum rating, si può affermare che

Da questo consegue che :

- la condizione migliore per pilotare un carico è tra il pin e la Vdd,

sfruttando la bassa resistenza dell' interruttore a canale N

- la condizione in cui si dissipa la maggiore potenza (persa per effetto

Joule sulla resistenza di conduzione) è con il carico tra il pin e la Vss

(interruttore a canale P)

I dati sono poi stati verificati con altre prove.

Ad esempio, il circuito

di pilotaggio del LED preso in considerazione all' inizio, va modificato così

:

- Per una Vdd = 5.00 V e un LED con Vled = 1.743 V (caso reale), una

resistenza in serie da 500 ohm produce una corrente di :

Iled = (Vdd-Vled)

/ R + Ron = (5 - 1,743) / 500 + 60 = 5.8 mA

1.6

Ovviamente, se si dovesse progettare con la massima sicurezza, si

dovrebbero applicare i parametri del foglio dati e il calcolo diventerebbe :

Iled = (Vdd-Voh-Vled)

/ R = (5 - 0.7 - 1,743) / 500 = 5.1 mA

1.7

il che non cambia molto le cose per il LED , ma è comunque un risultato

assai diverso dal calcolo iniziale della 1.0.

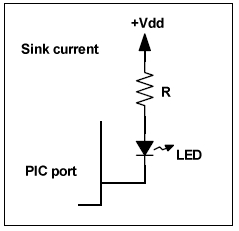

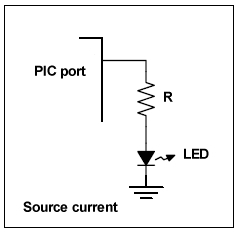

Allora meglio sink o source ?

|

Non esiste un "meglio" assoluto : dipende dall' applicazione.

Come le logiche TTL i port lavorano meglio in modo sink, sulla più bassa

caduta di tensione dei MOS a canale N, ma la differenza è trascurabile per la

più ampia parte delle applicazioni. Anche perchè può essere importante la

logica di comando.

|

Col carico collegato alla Vdd, la

"logica" del comando è , in un certo senso,

"invertita"

in quanto:

per accendere il LED occorre portare a 0

il livello del pin.

| Pin |

LED |

| 0 |

acceso |

| 1 |

spento |

|

|

Nel caso di un carico verso la massa, la

"logica" è più immediata; infatti:

per accendere il LED occorre

portare a 1 il livello del pin.

| Pin |

LED |

| 0 |

spento |

| 1 |

acceso |

|

La resistenza sarà calcolata con la 1.4 .

Nel primo caso (sink current) sarà da considerare per sicurezza la cdt di 0.6 V (param D080).

Nel secondo caso (source current) sarà da considerare la cdt di 0.7V (param

D090).

All' atto pratico, si potrebbe commentare con un bel "chissene" : se nel LED

passano 6 mA (1.2) piuttosto che 5.8 mA (1.6) o 5.1 (1.7) è del tutto irrilevante; la

luminosità del LED non avrebbe una differenza apprezzabile a vista e la

differenza tra le correnti sarebbe minore di quella possibile nel campo delle

tolleranze di LED, resistenza, tensione di alimentazione e caratteristiche del

PIC.

Più approfonditamente, si deve affermare che

- i 25 mA sono un reale limite massimo che non è particolarmente

conveniente considerare sempre sfruttabile, in quanto potrebbe anche non

essere fattibile e comunque sottopone il chip a stress non indifferente.

- i port in uscita digitale funzionano ottimamente per ambiti di correnti

inferiori

ovvero, se si devono comandare carichi con esigenze particolari, non si

potranno alimentare direttamente dai pin del PIC, ma occorrerà inserire

un qualche drive, ad es. un buffer o un generatore di corrente costante, un

open collector o open drain simili.

Però tra 10 mA della 1.0 e 5.1 mA della 1.7 qualche differenza c'è anche per il

povero LED : aspettarsi 10 mA e averne solo 5 a volte può essere eccessivo.

Il considerare correttamente la Ron degli switch MOS interni permette almeno

di non toppare troppo la scelta delle resistenze serie, sopratutto per carichi

ai limiti della capacità del pin.

A cosa serve, in conclusione, questa ricerca ?

Principalmente a tre cose :

- cercare di superare quella superficialità e approssimazione

che pervade

ogni componente della nostra società e che ha nel WEB il massimo esempio

- indicare che la valutazione della corretta resistenza di limitazione per

un carico di un pin dipende da molti fattori dei quali, sopratutto se è

richiesta una certa precisione, va tenuto conto

- individuare il limite dei 25 mA come un Absolute maximun rating

e

non una caratteristica di lavoro da dare per buona e sfruttare in ogni

circostanza

Riguardo a questo terzo punto, peraltro, i fogli dati indicano chiaramente

(a volerli leggere !) che :

- i 25mA sono applicabili ad ogni pin, ma con il limite di una massima

corrente complessiva assorbita dal chip non superiore a 200 mA !

Si tratta di un Absolute

Maximum Rating, quindi un valore massimo che non è opportuno superare

pena la distruzione del chip stesso.

Questo vuol dire che si potranno teoricamente prelevare 20 mA da 10 pin , ma non sarà

possibile disporre di 25 mA per più di 8 pin.

Questo è comunque inteso per operatività nei limiti di temperatura indicati,

in quanto l' energia persa nelle cadute di tensione interne al chip viene

trasformata in calore per effetto Joule e l' aumento del calore produce nei

semiconduttori una variazione della resistenza di conduzione, che spesso

avvia l' effetto di run down termico , con il

conseguente rischio di una distruzione del chip o di parte di esso.

Anche perchè i pin non dispongono di limitazione della corrente, per cui, anche se essa è limitata dalle impedenze interne, un corto circuito

tra un pin di uscita e la tensione di alimentazione, sopratutto se prolungato,

tenderà a creare

situazioni in cui il chip viene danneggiato in modo permanente. E, dai dati

rilevati, la conduzione di correnti vicine, se non oltre il limite dei 20 mA

creano surplus di effetto Joule con percentuale superiore anche al 50%. Diversa

potrà essere la condizione in cui il pin viene usato per un comando a

impulsi, dove esiste un tempo di non conduzione che permette al calore di

essere dissipato, ma si tratta di situazioni sempre da verificare .

Per esempio nei drive di display senza resistenze di limitazione, per quanto l' impulso di

Ton possa essere breve, la corrente istantanea

sarà comunque molto elevata e se nei fogli dati non ci sono molti elementi che

permettano di autorizzare con sufficiente sicurezza un simile approccio, si

richiede almeno di qualche misura più accurata che non il classico

"funziona e va bene così". Sarebbe opportuno applicare un buffer

sempre, in modo da far lavorare i pin in una condizione di sicurezza, sia come

corrente erogata sia come isolamento dal carico controllato, anche se questo aumenta il costo del circuito.

Soprattutto se si tratta di applicazioni in cui è richiesta la massima

affidabilità. Ma anche nell' utilizzo di buffer, va usato il "granum

salis": ad esempio, i pin dei processori embedded difficilmente sono in

grado di pilotare direttamente il gate di grossi Mosfet, causa l'elevata

capacità intrinseca; si dovranno utilizzare dispositivi del genere previsto per

il comando con livelli logic (logic-level MOSFET) oppure interporre un gate

driver.

Certamente per comandare un LED o il segmento di un display si potrà fare a

meno di un buffer, ma non si può essere d'accordo con l' abolizione fanatica

di tutti i componenti oltre al PIC : andrà bene a scopo ludico, per giocare,

ma non per produrre qualcosa di serio.

Una realizzazione tanto per fare non è

l' approccio che si

potrà usare per un apparecchio in grado di lavorare nelle condizioni comuni

all' industria, o, se non peggio, su un veicolo o in altre applicazioni

critiche.

|