Queste pagine sono state scritte per fornire una visione di

insieme, ma sufficientemente dettagliata, di come sono strutturate le logiche

che stanno dietro ai pin del PIC.

Una conoscenza sufficiente di questa parte del microcontroller consente di

poterlo utilizzare al meglio e di evitare banali errori.

Usiamo senza problemi le funzioni di GPIO del microcontroller, come ingressi

e come uscite, ma quanti si sono chiesti cosa c'è dentro al chip, dietro a

questa apparentemente semplice funzione ?

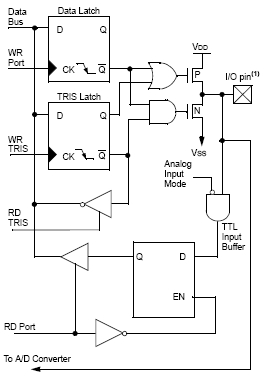

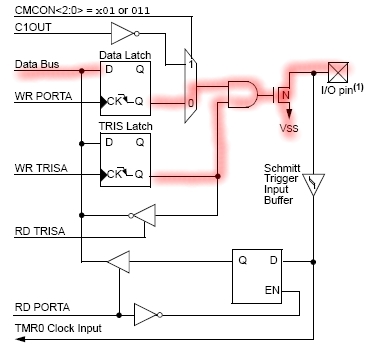

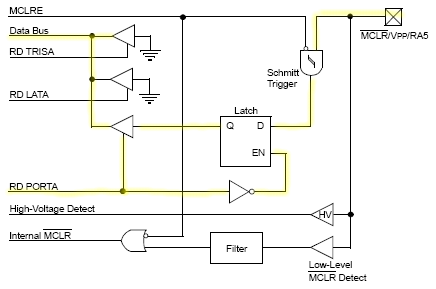

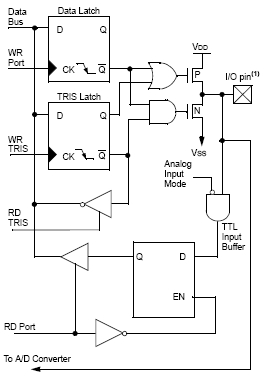

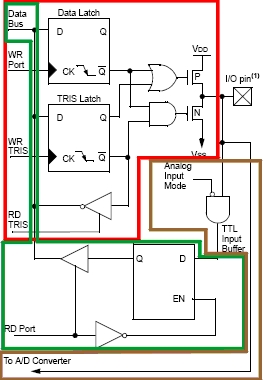

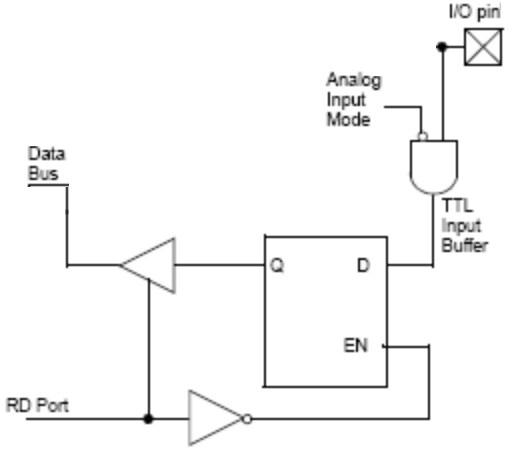

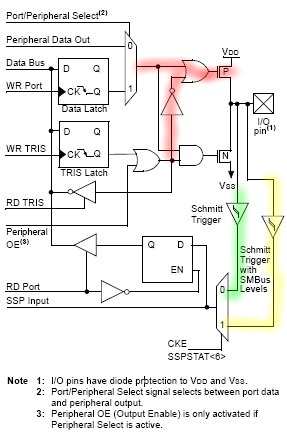

Il foglio dati del microcontroller (PIC16F87x) riporta uno schema di quello

sta dietro al pin.

|

Questo è un tipico port con la possibilità di assumere, sotto

controllo del programma, le funzioni di:

- uscita digitale

- ingresso digitale

- ingresso analogico

Microchip schematizza i circuiti che gestiscono le varie modalità

con funzioni logiche standard (AND, OR, Tri-state, flip-flop D) per

rendere comprensibile la logica di comando.

Questa circuiteria si ripete per ogni pin di I/O, con le variazioni

dovute alla possibilità di collegare al pin i vari moduli interni (USART,

TIMER, MSSP, HLDV, PWM, ecc).

Nel caso che vediamo qui, la funzione addizionale è quella di ingresso

analogico per il modulo AD converter.

|

|

| |

|

|

|

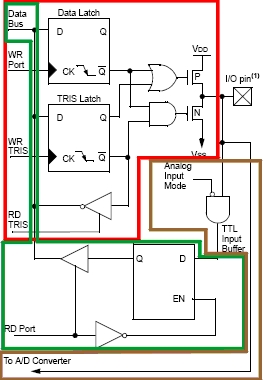

Possiamo evidenziare attraverso i colori le arre interessate dalle

varie funzioni.

- in ROSSO, l' area di

uscita: il bit di dato, reso sul Data Bus, è

condizionato dai segnali WR Port, WR Tris e RD Tris e reso al pin

attraverso una totem pole di transistor MOS

- In VERDE, l' area di

ingresso. Il segnale in entrata nel pin è

condizionato da un gate che seleziona la funzione analogica o quella

digitale. Viene poi latchato in un flip-flop e inviato al bus dati

- in MARRONE, l' area

analogica. Il segnale in ingresso viene

separato dal flip-flop dell' input digitale ed è istradato solo

verso il modulo AD

Il bus dati è comune, quindi, sia per il dato in uscita che per

quello in ingresso: la logica dell' I/O consente di applicare al bus

correttamente una o l' altra delle funzioni. Invece, il segnale

analogico arriverà sul bus dati solo dopo essere passato attraverso la

conversione effettuata dal modulo AD.

Vediamo ora nei dettagli la logica delle varie sezioni |

|

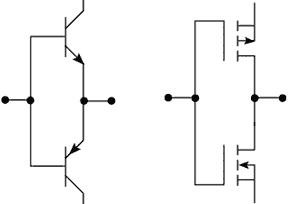

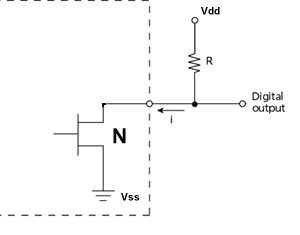

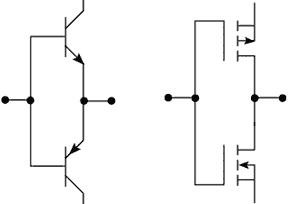

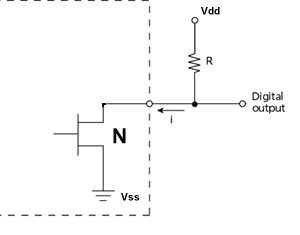

La sezione "di potenza" del pin configurato come uscita è

costituita da un totem pole di transistor MOS.

|

Se confrontiamo un totem pole di transistor BJT con uno di transistor

MOS possiamo rilevare che entrambi sono costituiti da due componenti

complementari, ovvero un PNP e un NPN a cui corrispondono

rispettivamente un MOS P e un MOS N.

La configurazione a lato ha in comune gli elettrodi di comando (basi

o gates) |

Il totem pole bipolare è non-invertente e non aggiunge alcun guadagno

in tensione, per cui, teoricamente, il suo tempo di commutazione è quello del

pre-driver che li comanda. Invece fornisce un guadagno di corrente, anche ampio,

che riduce l' impedenza di uscita e permette di azionare carichi capacitivi, sia

come source che come sink. Offe una velocità di commutazione media e non è

sempre adatto nel caso di alte frequenze.

Invece, alte frequenze di lavoro sono più facilmente raggiungibili utilizzando

componenti MOSFET complementari a canale P e N. A differenza dei BJT, il totem pole MOSFET offre un

guadagno di tensione che

migliora il tempo di salita e di discesa del segnale applicato. Particolare dei

MOS è l' avere il gate che presenta una caratteristica capacitiva, per cui

viene richiesta un forte impulso di corrente agli istanti di commutazione per

caricare/scaricare le capacità dei gates, dopo di che la corrente di

mantenimento è praticamente nulla.

Nella configurazione a gate in comune, questo totem pole è invertente

| Livello

Gates |

N |

P |

Livello Pin |

| Vdd - H |

conduzione |

blocco |

L |

| Vss - L |

blocco |

conduzione |

H |

Se si applica la Vdd, si ottiene la chiusura dell' interruttore N, che

collega il pin comune al GND; se si applica la Vss, si chiude l' interruttore P,

che collega il pin alla tensione positiva.

Il gate in comune assicura che sia impedita la conduzione di entrambi i MOS, il

che porterebbe ad un corto circuito tra la Vdd e la Vss, data la bassissima

resistenza interna dei semiconduttori.

Si osserva, però, che se i gate sono in comune, non esiste la

possibilità di bloccare entrambi i commutatori, per cui il pin di uscita potrà

solo seguire a livello basso o alto lo stato dei gates.

Poichè il pin deve poter supportare anche la funzione di ingresso, occorre

fare in modo che il due MOS possano essere bloccati entrambi.

Altrimenti la Vss o la Vdd sarebbero sempre presenti sul pin, impedendo

qualsiasi funzione di ingresso e con il rischio di danneggiare sia i MOS che il

circuito esterno.

Immaginiamo che il MOS P sia in conduzione: questo collega il

pin alla Vdd, limitando la corrente alla sola resistenza interna del MOS. Se

applicassimo all' ingresso un segnale a livello basso, si creerebbe un corto

circuito. E così pure se per il MOS N in conduzione con un livello alto

applicato.

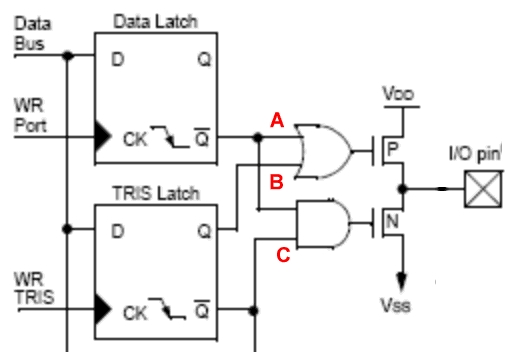

Questa possibilità di blocco di entrambi i commutatori è ottenuta con due

gate, un AND e un OR.

|

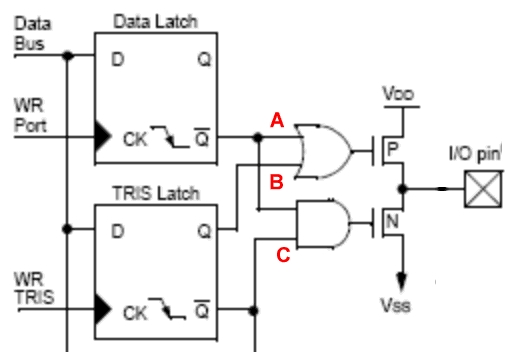

Se torniamo allo schema iniziale, osserviamo che i gate dei MOS non

sono in comune, ma sono comandati ognuna separatamente attraverso due

funzioni logiche:

- un OR comanda il MOS a canale P

- un AND comanda il MOS a canale N

Che cosa è che deve impedire ai MOS di condurre ?

E' lo stato del bit di direzione contenuto nel registro TRIS.

Questo bit stabilisce se il pin è una uscita (MOS abilitati) o un

ingresso (MOS bloccati). |

Il livello logico del dato in uscita, preso da Data Bus, viene caricato nel

Data Latch con il segnale WR Port, generato ad esempio da una istruzione BCF

(dato = 0) o BSF (dato = 1). Osservare come venga impiegata l' uscita del latch

Q negato, che presenta un valore opposto a quello del dato caricato.

| Opcode |

Data

Bus |

Data

Latch |

segnale A |

| Q |

Q/ |

| BCF

PORTx, n |

0 |

0 |

1 |

1 |

| BSF PORTx, n |

1 |

1 |

0 |

0 |

Il bit della direzione della porta arriva pure esso attraverso il Data Bus e

viene caricato nel TRIS Latch a seguito del segnale WR TRIS, generato da una

istruzione che scriva questo registro, ad esempio BCF TRISx, n. Osservare che

qui sono utilizzate entrambe le uscirte del latch, dirigendo quello non

invertita, Q, all' OR (segnale B) e quella invertita, /Q, all' AND (segnale C).

| Opcode |

Data

Bus |

TRIS

Latch |

segnale B |

segnale C |

| Q |

Q/ |

| BCF TRISx, n |

0 |

0 |

1 |

0 |

1 |

| BSF

TRISx, n |

1 |

1 |

0 |

1 |

0 |

L' uscita dell' AND comanda il gate del MOS a canale P; l' uscita dell' OR

comanda il gate del MOS a canale N.

I bit di TRIS e Dato sono conservati nei latch relativi.

| TRIS Latch |

Data Latch |

segnale A |

segnale B |

segnale C |

uscita OR

A | B |

uscita

AND

A + C |

MOS

P |

MOS

N |

pin |

| 0 |

0 |

1 |

0 |

1 |

1 |

1 |

blocco |

conduzione |

L |

| 0 |

1 |

0 |

0 |

1 |

0 |

0 |

conduzione |

blocco |

H |

| 1 |

0 |

1 |

1 |

0 |

1 |

0 |

blocco |

blocco |

- |

| 1 |

1 |

0 |

1 |

0 |

1 |

0 |

blocco |

blocco |

- |

Il bit di TRIS, conservato nel TRIS Latch, a livello 1 blocca i MOS e

abilita la funzione di ingresso. Se entrambi i MOS sono bloccati, la loro

resistenza interna è estremamente elevata e nessuna corrente viene emessa sul

pin, che può ricevere così un segnale dall' esterno.

Il bit di TRIS a livello 0 abilita i MOS e la funzione di uscita. In

questo caso, il livello del bit di dato viene passato in uscita e manda in

conduzione uno dei due MOS.

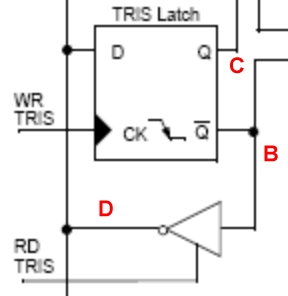

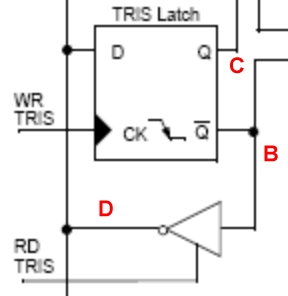

Il valore del bit scritto nel TRIS Latch può essere riletto con un semplice

meccanismo

|

Un gate tri-state riceve in ingresso il segnale B, che corisponde al

valore negato del bit di TRIS conservato nel TRIS Latch.

Il gate è invertente e la sua uscita D è collegata al bus dati.

Abilitando il gate con il segnale RD TRIS, generato, ad esempio, a

seguito di una istruzione

MOVF TRISn, W

il livello B invertito passa sul Data Bus per essere letto dall'

unità centrale. |

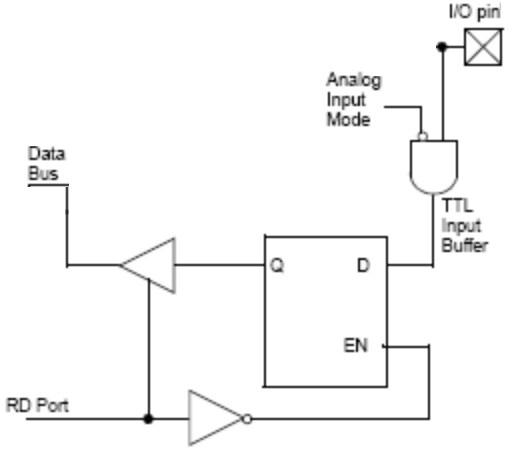

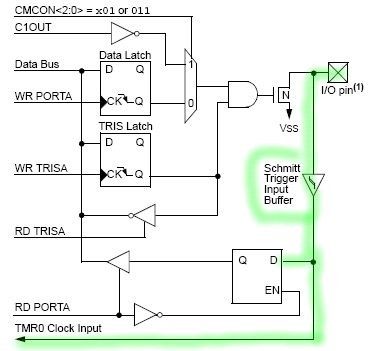

La logica di ingresso è molto semplice

|

Il segnale proveniente dall' esterno e applicato al pin viene

condizionato da un gate AND.

Se è selezionato il modo Analogico, il gate impedisce al segnale di

ingresso di proseguire verso il latch. Un livello Analog Input Mode

arriva dal registro ADCON ed è applicato ad un ingresso invertente

dell' AND.

Analog

Mode |

inv.

input |

I/O

pin |

TTL

In buffer

uscita |

| 0 |

1 |

1 |

1 |

| 0 |

1 |

0 |

0 |

| 1 |

0 |

1 |

0 |

| 1 |

0 |

0 |

0 |

|

Ovvero, se il bit di Analog Mode è a 0, il livello del pin di IO è

applicato all' ingresso D del latch.

L' uscita Q del latch è abiltata dal segnale RD Port, invertito; questo segnale

è generato, ad esempio, a seguito di una istruzione BTFSC PORTx, n.

Il RD Port ha anche la funzione di abilitare un gate tri-state che mette in

comunicazione l' uscita Q del latch con il Data Bus, trasferendo così lo stato

del pin all' unità centrale.

Se osserviamo lo schema complessivo iniziale possiamo notare che la funzione

di ingresso digitale è sempre attiva in concomitanza con quella di uscita

digitale. Questo permette di leggere lo stato effettivo del pin, sia che si

tratti di un segnale esterno, sia che si tratti dello stato imposto dai MOS in

uscita. La lettura dello stato del pin in condizioni di uscita digitale attivata

è indispensabile per le operazioni di modifica dello stato del bit tramite una

operazione di scrittura come ANDLW o ADDWF.

Questo perchè il sistema impiegato nei PIC è quello detto R-M-W

Per ovviare al problema dell' R-M-W, nei PIC enhanced è stata implementata

una struttura leggermente diversa, ma fondamentalmente efficace.

|

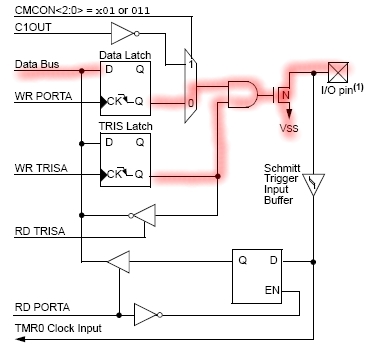

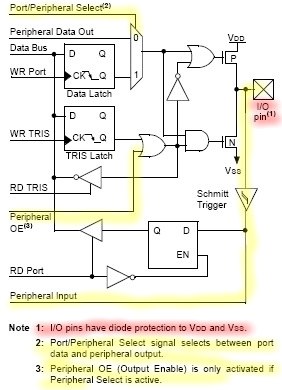

Se osserviamo la differenza con lo schema iniziale, quello dei PIC

mid-range, notiamo immediatamente che si è aggiunto un gate tri-state

che mette in comunicazione l' uscita Q del Data Latch con il bus dati

(evidenziato in rosso).

Questa connessione permette di leggere NON lo stato del pin, ma lo

stato del latch e quindi evitare il problema dell' R-M-W.

L' abilitazione RD LATx viene fornita da una istruzione che legge il

registro di LAT, ad esempio BTFSC LATx, n.

Si può osservare dallo schema la differenza tra la lettura di LAT e

quella di PORT:

- leggendo PORT si abilita RD Port come visto prima, quindi si

collega al bus il livello fisico del pin in quell' istante

determinato (circuito blu)

- leggendo LAT, invece, si legge lo stato del Data Latch, prima del

buffer di uscita (circuito rosso)

Per quanto riguarda la scrittura, una operazione diretta a LAT è in

effetti diretta al Data latch, quindi:

BSF LATx, n è del tutto identico a

BSF PORTx, n |

Maggiori dettagli sul problema R-M-W sono presentati qui.

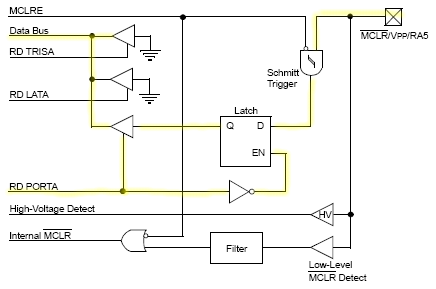

Da quanto abbiamo visto finora è facile capire come funziona il meccanismo

dell' ingresso analogico.

|

Se ci rifacciamo a quanto detto prima a riguardo del PORT come

ingresso, il segnale Analog Input Mode inibisce il gate AND del

TTL Input Buffer e collega direttamente l' IO pin al modulo AD (circuito

giallo).

V anno osservate alcune particolarità:

- la modalità di ingresso Analogico esclude quella di ingresso

digitale, ma non quella di uscita digitale

- il canale di ingresso verso il modulo AD può essere in comune con

altre funzioni, come ad esempio li moduli HLVD e i comparatori

Il primo punto indica che è possibile avere il pin configurato come

out digitale e nello stesso tempo aver attivato l' ingresso del modulo

AD.

Ovviamente questa configurazione è da evitare assolutamente sia

perchè il modulo AD leggerebbe solo il livello alto o basso applicato

dal buffer MOS al pin, sia perchè si rischierebbe di danneggiare sia

il buffer che il circuito esterno se i livelli di tensione sono tali

da far circolare forti correnti, limitate solo dalla resistenza di

conduzione dei MOS.

Per cui è indispensabile configurare come input i pin che si vogliono

usare come ingressi AD: la configurazione come input blocca il buffer

MOS. |

In generale, per evitare problemi di conflitti tra segnali di ingresso al

chip e segnali in uscita è opportuno inserire, in fase di sviluppo, delle

resistenze di basso valore (100 ohm o più) in serie ai pin del micro. Queste

resistenze, se non in casi estremi, non disturbano il funzionamento del

circuito, ma limitano la corrente nei casi in cui sia il PIC che il circuito

esterno cerchino di inviare corrente o siano in condizioni da creare corti

circuiti.

Questa situazione capita quando si utilizza, ad esempio, una comunicazione

seriale a 1 filo verso una periferica e si richiede il cambio di direzione del

pin da ingresso a uscita: in questa situazione è possibile che per istanti più

o meno lunghi sia il PIC che la periferica cerchino di alimentare la connessione

o si trovino a livelli opposti. La cosa può non avere effetto se i tempi di

commutazione della direzione sono a livello di ciclo di istruzione, ma se per

caso il debug viene arrestato in questa condizione o il firmware non perfetto la

consente, sono possibili danni al port e/o alla periferica.

Una volta fissato il progetto e consolidato il firmware, queste resistenze

possono essere eliminate.

Il secondo punto indica che è possibile attivare contemporaneamente sulla

stessa linea linea di ingresso il canale AD e, ad esempio, l' HLVD, che ricevono

entrambi lo steso segnale analogico.

Evidentemente sarà necessaria una sorgente del segnale analogico con impedenza

molto bassa per poter pilotare entrambi i carichi nei termini che il foglio dati

impone.

Altri PIN

Alcuni pin hanno anche altre funzioni applicabili e non tutti i pin hanno le

stesse possibilità.

Ad esempio, nelle immagini usate per la descrizione precedente, si fa

riferimento ad un PORTA, dove, nel caso di RA5, oltre alle funzioni digitale e

analogica, esiste anche quella si Select per il modulo MSSP.

Sarà sempre necessario consultare il foglio dati per rilevare quali

impostazioni sono possibili e su quali pin e port.

|

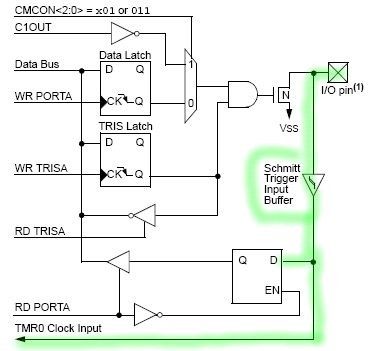

Un cenno particolare si può fare a riguardo del pin RA4

(PORTA,4) che generalmente ha un buffer di uscita costituito dal solo

MOS N, ovvero un Open Drain.

Qui vediamo il particolare del PORTA, 4 preso dal foglio dati di un

mid-range (16F876/77), ma la descrizione è valida per i PIC in

generale.

Si nota immediatamente la mancanza del MOS P, per cui la

logica di comando è ridotta al solo gate AND e funziona come visto più

sopra (circuito rosso).

Come visto prima, il livello logico imposto al bit di TRIS stabilisce

se è attiva l' uscita oppure è bloccata per avere solo ingresso.

Qui, il pin supporta anche le funzioni di uscita del comparatore e del

CCP1, per cui si è aggiunto uno switch che, programmato a livello 0

abilita la funzione digitale e a livello 1 abilita gli altri moduli di

uscita. |

Va da se che per usare le funzioni C1OUT e CMCON è necessario che il pin sia

configurato come uscita: lo switch aggiunto isolerà il Data Latch.

|

Se il totem pole poteva comandare sia carichi collegati al positivo

che carichi collegati alla massa, l' open drain può comandare

solamente carichi collegati al positivo (sink current, indicata dalla

freccia i).

Quindi un LED collegato tra il pin e la Vss non potrà

accendersi. Sarà necessario collegarlo tra il pin e la Vdd.

Se si deve derivare un segnale logico dal pin, occorre inserire un

pull-up tra il pin e la Vdd, altrimenti non si avrà livello logico.

|

Altra nota importante è che questo open drain non è previsto per avere

applicata tensione superiore alla Vdd; quindi non è possibile

azionare carichi a tensioni superiori.

|

Nel caso esemplificato, il pin ha anche funzione di ingresso per il

clock del Timer0 (TMR0 Clock Input).

A questo scopo si è aggiunto uno Schmitt Trigger per fornire livelli

di commutazione adeguati ad un ingresso "sensibile".

La caratteristica del trigger è quella di commutare il suo stato di

uscita solo a ben precisi livelli della tensione di ingresso

(caratteristico diagramma di uscita con isteresi), fornendo un segnale

quanto possibile "pulito" e senza incertezze al clock.

Dato che il trigger è inserito subito dopo al pin di IO (circuito

verde), il trigger è efficace anche quando si utilizza il

normale ingresso digitale, dato che la sua uscita comanda in comune

sia il TMR0 Clock Input che l' ingresso D del latch di lettura. |

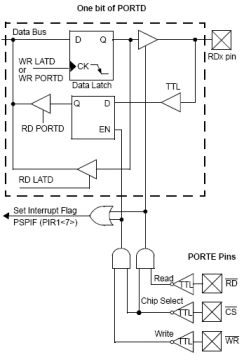

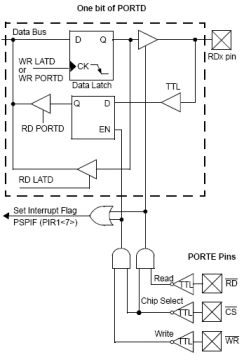

Il PORTD solitamente supporta la funzione PPS

|

Paralle Port Slave è una modalità che permette di inserire il

PIC come periferica (slave) del bus di un microprocessore.

I dati sono scambiati tra PIC e host su un bus a 8 bit, controllato dai

classici segnali di Write negato, Read negato e Chip Select negato.

Diventa necessario gestire i segnali di sincronismo del bus dell'

host, per cui alcuni pin di PORTE vengono dedicati ai segnali /RD, /WR

e /CS, che , attraverso una semplice logica di AND abilitano al

direzione dei dati sul pin.

/WR assieme a /CS abiliterà la scrittura dei dati e /RD con

/CS la lettura.

Una logica OR deriva questi segnali per attivare, se abilitata, una

chiamata di interrupt per una gestione non in polling.

Per una precisa commutazione, gli ingressi dei segnali di controllo

del bus hanno un Trigger di Schmitt in serie.

Il resto della logica del PORT è analogo a quanto finora visto. |

|

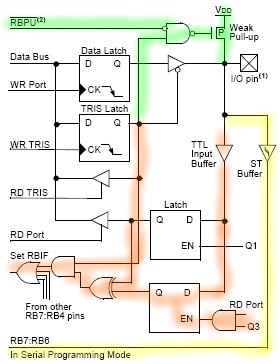

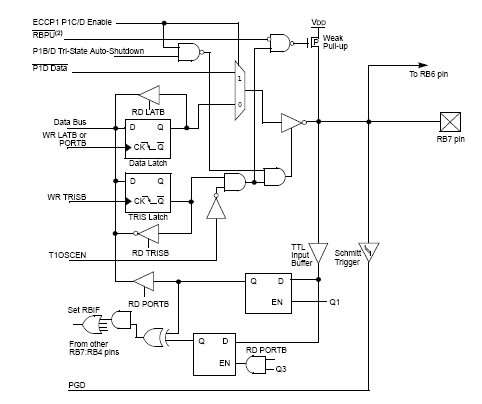

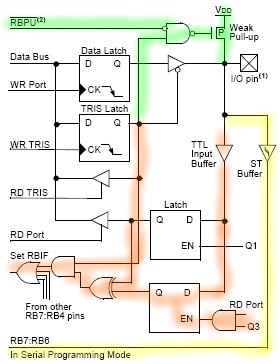

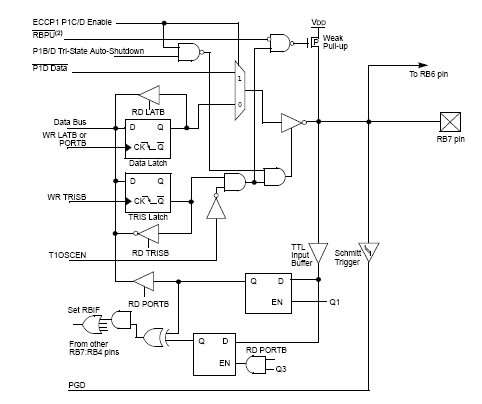

Più complicata è la logica di controllo dei pin del PORTB che

dispongono di:

- pull-up programmabile (circuito verde)

- interrupt al cambio di stato (circuito

rosso)

- funzioni di comunicazione per la programmazione (circuito giallo)

Si può capire facilmente la logica del Weak Pull-up: si

tratta di un pull-up. ovvero di una resistenza che collega la linea alla

Vdd, realizzata non con componenti passivi, ma con interruttori MOS

costruiti con una resistenza interna elevata (attorno a 100 k).

Un gate AND riceve il bit /RBPU e comanda il pull-up solamente

se la funzione impostata è quella di ingresso (se l' uscita Q del TRIS

Latch è a 1, il buffer tri-state -qui semplificato come un gate non

invertente- in uscita è bloccato e il pull-up dipende da /RBPU. Se il Q

è a livello 0, il buffer è abilitato mentre il pull-up non è

inseribile, qualunque sia il valore di /RBPU). |

Da notare che /RBPU entra in un terminale invertente dell' AND e

quindi la sua logica è rovesciata, ovvero:

Una logca più complessa, che utilizza un latch e diversi gate (2 AND, un

EXOR e un OR finale che mixa i segnali provenienti dai vari pin) consente di

inviare sulla linea di interrupt una chiamata alla variazione di stato del pin.

I segnali Q1 e Q3 sono relativi alle transizioni di clock (4) che servono al

completamento di un ciclo della CPU.

La funzione di In Serial Programming (ICSP/ICD), che ha un ingresso a

trigger dedicato, viene selezionata non a livello di registri della porta, ma di

configurazione iniziale (DEBUG= ON/OFF; LVP=ON/OFF).

|

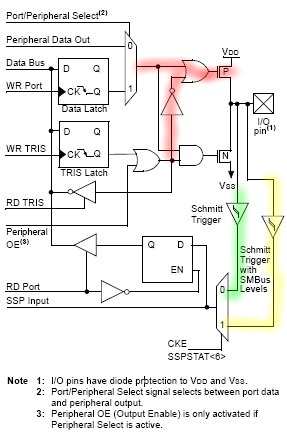

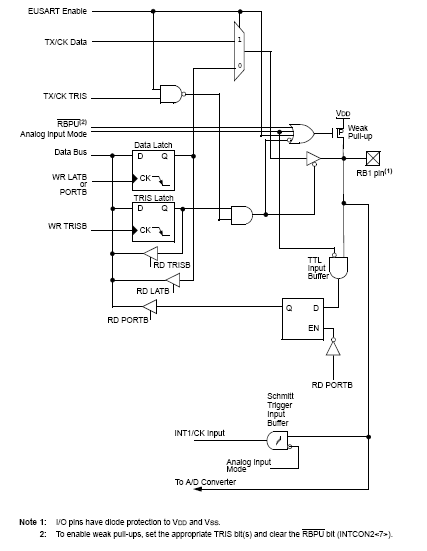

I pin di PORTC hanno funzioni speciali collegate al modulo MSSP

e all' USART.

Se per quest'ultimo non ci sono particolari esigenze, a parte un

trigger in ingresso per ripulire il segnale, l' uscita e l' ingresso

dell' MSSP in modalità I2C richiede diverse variazioni.

In primo, luogo I2C è un bus con pull-up esterno sulla linea.

Questo richiede driver open drain.

A questo scopo, un gate addizionale (circuito rosso) trasforma il totem

pole in uscita a singolo transistor, escludendo il MOS P.

In ingresso, invece, ci sono due trigger distinti, uno per i

livelli I2C e uno per i livelli SMBus. Infatti le due

modalità, pur essendo analoghe come protocollo, utilizzano livelli

logici differenti che non sarebbero facilmente distinguibili da un

trigger unico. Quindi Microchip ha optato per la realizzazione di due

diversi.

I segnali di uno solo dei due canali, selezionati da uno switch

comandato dal bit 6 di SSPSTAT, sono inviato al' ingresso SSP

Input del modulo MSSP.

Questa connessione è in comune con l' ingresso Q del latch di lettura

della modalità ingresso digitale.

|

|

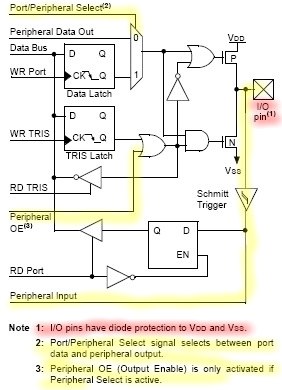

Analoga la situazione dei pin RB7:5, dove è il bit Port/Peripheral

Select ad effettuare il comando dello switch che seleziona tra dati

digitali e uscita delle periferiche interne.

In aggiunta a questo, un bit Peripheral OE (Output Enable),

assieme al TRIS Latch, abilita l' accesso all'uscita alle periferiche

(circuiti evidenziati in giallo).

Anche qui, dato che si tratta di segnali di comunicazione seriale, l'

ingresso prevede un Trigger di Schmitt.

Un appunto riguarda una nota (1) evidenziata in rosso, che

appare vicino al quadrato barrato che rappresenta il pin.

Questa nota fa riferimento alla presenza di diodi di protezione

del pin dalle tensioni inverse o superiori/inferiori alla tensione di

alimentazione e che possono essere verso la Vss e la Vdd o solo verso la

Vss. |

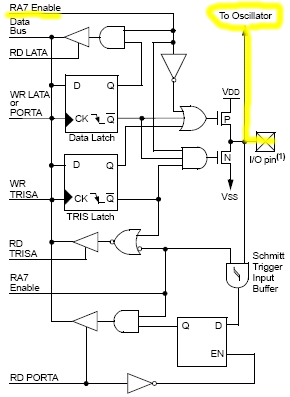

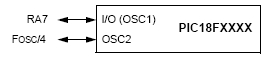

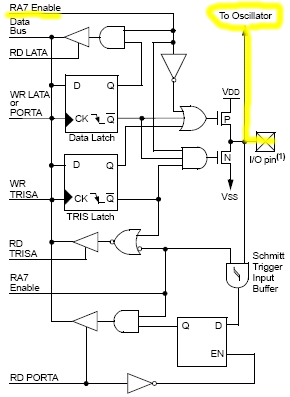

Più complessa è la struttura dei pin a cui fanno capo sia

finzioni GPIO che oscillatore:

|

Questo è lo schema di principio del pin RA7 nel PIC18F1220/1320.

Questo pin fa parte del sistema dell' oscillatore esterno, in genere

assieme a RA6.

Una maggiore complessità nell' abilitazione del port consente di

indirizzare la funzione del pin all' oscillatore.

Per le modalità LP, XT, HS, la coppia RA7/RA6 è utilizzabile con

componenti esterni (quarzo, condensatori, resistenze).

Da notare come in modalità SLEEP il gate dell' oscillatore possa essere

bloccato per minimizzare il consumo. |

|

|

Sono poi possibili altre configurazioni dell' oscillatore, che

interessano in modo diverso i due pin:

|

Modo RC.

Il clock è stabilizzato da un gruppo RC esterno applicato a RA7,

mentre su RA6 è disponibile il clock / 4. |

|

Modo RCIO.

Il clock è stabilizzato da un gruppo RC esterno applicato a RA7,

mentre RA6 può essere utilizzato come GPIO.

|

|

Modo EC.

Il clock arriva da una sorgente esterna. Deve avere le

caratteristiche spcificate sul foglio dati. In questo caso la logica del

port funge solamente da gate per trasferire il segnale al resto del

circuito.

Il pin RA6 riporta all' esterno il clock/4. |

|

Modo ECIO

Il clock arriva dall' esterno, come sopra e il pin RA6 è

utilizzabile come GPIO. |

|

Modo INTIO1.

Il clock è generato dall' oscillatore interno. Su RA6 è disponibile

il clock/4 e RA7 diventa un GPIO. |

|

Modo INTIO2.

Il clock è generato dall' oscillatore interno. RA6 e RA7

diventano GPIO. |

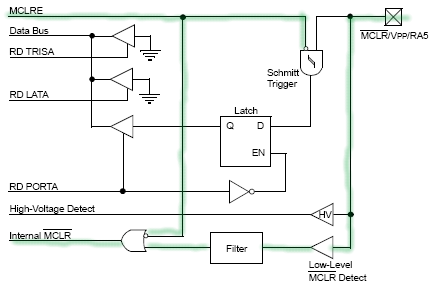

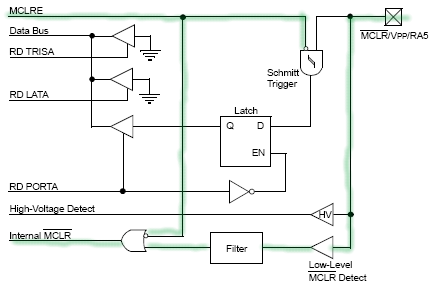

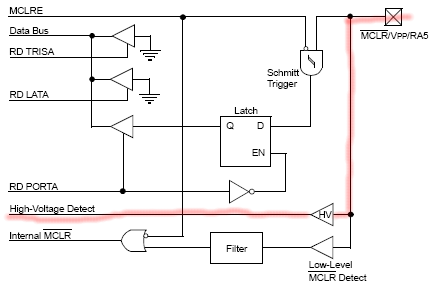

Il pin del Master Clear può assumere varie funzioni:

-

Master Clear - reset esterno

-

GPIO - solitamente un port RE

-

Ingresso dalla Vpp durante la programmazione HV

|

La struttura della logica che sta dietro il pin è schematizzata a

lato.

E' stata evidenziato in verde il percorso del segnale del reset

esterno:

- Il segnale, dal pin arriva ad un gate di rilevamento (Low-Level

Detect) a cui fa seguito un filtro per attenuare eventuali disturbi;

- dopo il filtro, un gate OR è abilitato dal segnale di

configurazione MCLRE (invertito) e trasferisce il livello di reset

alla logica successiva.

|

|

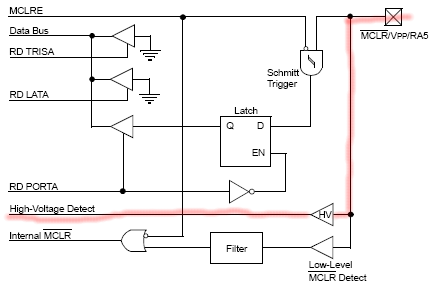

Durante la programmazione HV (con tensione superiore a quella di

alimentazione), questa tensione viene applicata al pin MCLR.

Un gate di rilevamento dell' alta tensione permette a questo livello

di passare alla logica di scrittura della memoria programma e della

EEPROM. |

|

Se la configurazione esclude la funzione di MCLR, portando a 1 il

segnale MCLRE, il pin può essere impiegato come un GPIO, ma solo come

ingresso.

In giallo è evidenziata la circuiteria interessata.

- All' ingresso fa seguito un trigger di Schmitt che ripulisce il

segnale e lo invia ad un latch.

- Il latch viene letto abilitando il segnale RD PORTx, di cui il pin

diventa parte.

|

Gli schemi qui sopra sono relativi al PIC18F1320, dove MCLR può

diventare RA5. Per altri processori, MCLR solitamente diventa RE3.

Alcuni pin sono programmabili come uscite o ingressi di moduli

interni di comunicazione (UART, MSSP, ICSP-ICD, ecc.).

|

Questo è il pin RB7 del PIC18F1320.

In questo caso le funzioni associate sono molteplici:

- GPIO

- ECCP1

- T1OSCEN

- ICSP - PGD

- RB Pull-up

- Interrupt del PORTB

La logica permette di scambiare le varie funzioni a seconda delle

impostazioni dei registri di controllo.

Va notato il trigger sull' ingresso PGD per ripulire il segnale. |

|

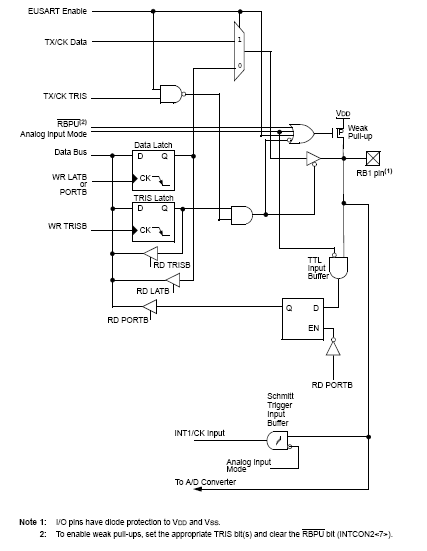

Un altro esempio di port complesso è RB2, sempre dal PIC18F1320.

In questo caso al port convergono:

- GPIO

- EUSART (TX)

- AD converter

- RB Pull-up

- CK input

- interrupt INT1

Anche qui la logica permette di scambiare le varie funzioni a seconda

delle impostazioni dei registri di controllo.

Si può osservare come i weak pull-up siano realizzati con componenti

attivi (MOSFET a canale P a resistenza di conduzione elevata) e non con

componenti passivi. |

Esiste poi un' ampia varietà di PIC con funzioni particolari,

come driver per LCD, USB, ecc) con scehm più o meno complessi, che per analogia

con quanto visto finora, non dovrebbe essere difficile interpretare.

-

Questa pagina vuole essere solamente una vista d'

insieme della struttura tipica dei port di un PIC generico.

Le particolarità specifiche di ogni port devono essere

identificate leggendo con cura il foglio dati di ogni

componente, in quanto non tutti i processori hanno le stesse

disponibilità, configurazione e funzione dei port e tra processore

e processore, sopratutto se di famiglie diverse, possono esserci

differenze anche sensibili nelle funzioni supportate.

-

Uguale necessità riguarda la situazione dei port

al reset (default), che può variare a seconda delle famiglie.

Il non considerare questi punti porta all'impossibilità di

utilizzare correttamente i pin.

-

Si ricorda di nuovo che normalmente RA4 è un

open drain e quindi non può comandare carichi alla Vss, oltre a

non sopportare tensioni superiori alla Vdd.

-

Si ricorda che i pin utilizzati come ingressi

analogici vanno settati come input nei TRIS

corrispondenti

-

I Weak Pull-up di PORTB sono pull-up attivi

e, anche se raramente, possono trovare incompatibilità se gli

ingressi sono pilotati da alcuni tipi di circuito esterno, in

particolare se è richiesto dal pull-up una corrente ben

determinata.

-

Informazioni più dettagliate sul problema dell'

R-M-W sono disponibili in altre pagine dei T&T

|

|