Un semplice I/O expander I2C.

Dove sia necessario disporre di I/O su un bus I2C, il chip PCF8574

offre una soluzione semplice dal punto di vista della gestione.

Si tratta di un array di 8 bit che il costruttore (NXP e Texas) definisce

"quasi-bidirectional".

Sotto questa strana definizione si nasconde una struttura molto

semplice, ma anche efficace, la cui comprensione, però, richiede una attenta

lettura del foglio dati, oltre ad una certa conoscenza dell'elettronica.

Per superare questi ostacoli e rendere utilizzabile il componente alla

maggioranza degli utenti, vediamo di descriverlo nel dettaglio.

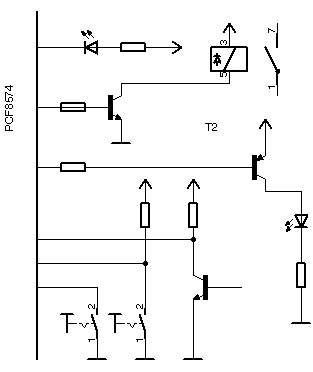

Il foglio dati offre un diagramma semplificato del componente, che è

disponibile in vari packages (SOIC, VQFN, TSSOP, TVSOP, compreso un DIP a 16

pin).

Si interfaccia con il bus I2C attraverso i soliti SDA/SCL, per un clock fino a

100kHz.

A questi segnali si

aggiunge una linea INT.

Si tratta di una uscita open drain che va a livello basso ogni volta che

è rilevata una variazione di stato sull' I/O port (come ingressi). Questo è utile per informare il microcontroller che è avvenuto un evento in

ingresso. Il comando della linea INT è dipendente dal PCF8574 ed è una

"iniziativa" che la periferica determina autonomamente. Non è

mascherabile e quindi sta all' utente del microcontroller la gestione del

segnale. INT potrà essere collegato ad un I/O del microcontroller, ad esempio

uno dei pin che generano una chiamata di interrupt, in modo tale che il

programma possa prendere in carico l' evento nel modo più rapido ed efficace;

oppure collegata ad un I/O generico e interrogata in polling.

In ogni caso, dato che si tratta di un open drain, occorre una resistenza di

pull-up (valore

tipico 4K7-10k).

Linee INT di più dispositivi possono essere collegate in ORing; in questo

caso il microcontroller dovrà leggere tutti gli slave per verificare quale ha

effettuato la chiamata. Il reset di questo segnale avviene a seguito del ritorno del livello del pin

di I/O, che lo ha generato, al valore precedente o della lettura/scrittura del

port.

La linea INT è l' unica azione attiva direttamente comandata dal chip, che,

per il resto, è una periferica del tutto slave.

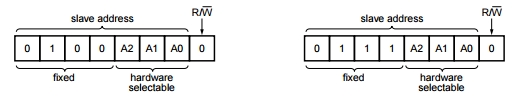

L' indirizzamento sul bus I2C è definito, come solito, da alcuni bit fissi

assegnati alla periferica a cui si aggiungono 3 bit

(A2:0) impostabili via hardware dall' utente. Le due versioni del chip

(PCF8574 e 8574A) si differenziano solamente per la parte dell' indirizzo pre

fissata nel chip stesso.

|

PCF8574

PCF8574A |

A seconda della configurazione del pin A0,1,2 il chip assumerà

i seguenti indirizzi:

Ricordiamo che il bit 0 dell'indirizzo a 7 bit vale 0 per la scrittura e 1 per la

lettura.

Risulta evidente che sarà possibile collegare su un solo bus 8 PCF8574 e 8

PCF8574A, per un totale di 128 I/O.

Il chip dispone esclusivamente di questo indirizzo e,

contrariamente a quanto ci si aspetti, non ha

alcun registro interno: da qui possiamo partire per comprendere la definizione

iniziale di "quasi-bidirectional".

In questo ci può essere di aiuto il diagramma semplificato dei port:

Il buffer in uscita è costituito dai soliti MOSFET P-N;

osserviamo, però, che, mentre il MOSFET N collega direttamente il pin di I/O al

GND, il MOSFET P ha in serie un generatore di corrente da 100uA: si tratta di

qualcosa di simile ad un weak pull-up. In sostanza:

-

se il port è impostato a livello basso, il pin è collegato

al gnd

-

se il port è impostato a livello 1, sul pin è applicato

questo livello, salvato nel FF dati, ma attraverso una resistenza elevata

Sostanzialmente, programmando il pin a livello 0 lo colleghiamo

direttamente al GND; programmandolo a livello 1 gli applichiamo un pull-up da

100uA.

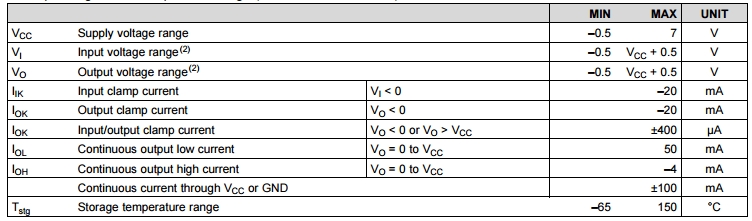

Questo è reso anche dalle caratteristiche elettriche (foglio

dati Texas):

Vediamo come la corrente assorbibile dal pin sia di 20mA a

livello basso, mentre di soli 4mA (1mA nelle specifiche di NXP) a livello alto.

Questo vuol dire che è possibile comandare direttamente carichi appesi alla Vcc,

come LED e piccoli relais, attraverso il MOSFET N che collega il pin a massa, mentre,

se si vuole sfruttare il livello alto, occorrerà un buffer, dato che il livello alto è gestito praticamente solo dal

weak pull-up.

Considerando il mA massimo delle specifiche NXP, occorrerà come buffer

o una porta logica a basso fan-in o transistor BJT con elevato guadagno (per

200mA in collettore con 1mA di base, occorre un guadagno superiore minimo di

200).

Nel caso in cui si comandassero MOSFET, va tenuto presente che la bassa

disponibilità di corrente finirebbe per limitare la frequenza massima di

commutazione.

In effetti il circuito è lievemente più complesso; riprendiamo

lo schema visto sopra evidenziando in rosso alcuni punti:

Al momento dell' impulso di scrittura, se il dato impostato è a

livello alto, viene attivato un MOSFET ausiliario che collega il pin con la Vcc.

La durata di questo collegamento diretto è limitata alla durata dell' impulso

di scrittura, ma è utile per iniettare una corrente maggiore di quella limitata

da weak pull-up.

Si tratta di un "acceleratore" o strong pull-up di corrente che

permette di superare i 100uA del generatore di corrente del MOSFET P.

La breve durata dell' impulso è necessaria per evitare problemi quando il pin

è impiegato come ingresso e viene tirato a livello basso. Al termine dell'

impulso il livello alto sarà mantenuto solo da generatore di corrente. Questo

consente di comandare anche piccoli MOSFET esterni senza problemi.

In questa struttura sta il trucco che determina il "quasi-bidirectional".

Se per comandare un pin in uscita basterà portarlo a livello

alto o basso (con i limiti descritti nella corrente in uscita), per usare lo

stesso pin come ingresso non occorre altro che portarlo a livello 1 !

In questo modo al pin è applicato il weak pull-up e il

circuito esterno ad esso collegato non dovrà fare altro che portarlo a livello

basso.

Infatti il latch di lettura, comandato dal relativo Read Pulse,

è sempre collegato al pin. Questo vuol dire che la lettura del PCF8574 renderà

sempre lo stato elettrico applicato ai pin.

Con questa soluzione si evita la necessità di un registro di

direzione.

Comandare PCF8574.

Da quanto sopra, il comando del PCF8574/A è estremamente

semplice:

-

scrittura di pin come uscita :

- inviare indirizzo con bit 0 = 0 (write)

- inviare il dato con il valore da assegnare al pin

-

lettura di pin come ingressi;

I pin che si vogliono usare

come ingressi saranno stati preventivamente scritti a livello alto :

questo applica il weak pull-up e permette ad un dispositivo esterno di

portare l'I/O a livello basso.

Quindi. basta:

- inviare indirizzo con bit 0 = 1 (read)

- leggere il dato che contiene il valore pari al livello di ognuno degli 8

I/O

Per i pin che sono usati come uscite, la lettura riporterà il

livello logico del pin.

Nel caso il cui si utilizzi la linea INT, questa andrà a

livello basso a seguito di un cambiamento di stato in un pin causato da un

segnale esterno. Si collegherà ad un I/O del microcontroller che gestisca un

interruzione esterna oppure ad un I/O generico da testare in polling.

La cancellazione del segnale avviene automaticamente leggendo/scrivendo il

PCF8754.

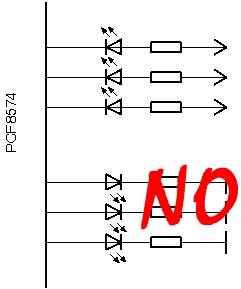

Collegare carchi e ingressi.

|

|

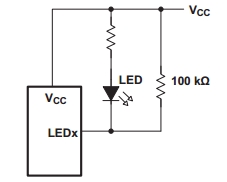

Per le caratteristiche di corrente, se si deve comandare LED,

questi andranno collegati tra il pin e la Vcc.

Ovviamente la resistenza di limitazione della corrente per ogni LED è

necessaria.

Collegandoli tra il pin e il GND non ci sarà sufficiente corrente

disponibile per accenderli. |

|

|

Nel caso in cui il carico assorba una corrente maggiore di 20mA, si

potranno collegare più pin assieme, avendo ovviamente cura di

commutarli tutti nello stesso istante. Nel comando di carichi esterni che assorbono corrente, va tenuto

conto del fatto che il chip ha un limite di corrente massima erogabile

complessiva,

che è pari a 100mA. Quindi si potranno, ad esempio, collegare non più

di 5 LED da 20mA ciascuno o 8 LED da 12.5mA ciascuno. |

|

|

Se si connette LED e chip alla stessa Vcc, va considerato che il è essenziale che la tensione

del MOSFET P sia superiore o uguale a VCC per ridurre al minimo il consumo di corrente.

La soluzione è aggiungere una resistenza di alto valore in parallelo al LED.

Questo mantiene la VI dell'I/O pari o superiore VCC e riduce il consumo

di corrente a LED spento.

La cosa può essere necessaria in applicazioni alimentate a batteria,

dove occorre minimizzare i consumi. |

|

|

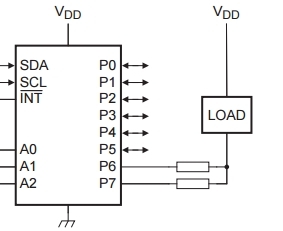

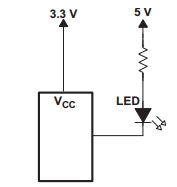

E' possibile, quindi, alimentare carichi con una tensione diversa da

quella del chip (sempre restando nei limiti delle caratteristiche,

ovvero tra 2.3 e 5.5V).

Ad esempio, è possibile usare una Vcc per il PCF8574 di 3.3V e una di 5V

per il LED (la Vcc del LED è maggiore alla Vcc del chip+VT del LED e il

MOSFET lavora in condizioni ideali).

|

|

In uno stesso chip si potranno utilizzare alcuni pin come input e

altri come output.

Non ci sono problemi nel collegare elementi logici CMOS o TTL e buffer

darlington del genere ULN o MOSFET tipo 2N7000 o piccoli BJT con almeno 200 di

guadagno.

Per quanto riguarda i segnali di ingresso, si potranno applicare

open collector/open drain, optoisolatori o contatti, per i quali può essere necessario

aggiungere un pull-up esterno dove richiedano una corrente maggiore dei 100uA

disponibili.

Si tratta di elementi che portano il pina a massa, quindi l'ingresso

attivato sarà riconosciuto da un livello 0

Si potranno altresì collegare senza problemi tastiere a matrice,

moduli display LCD, opto per comando di TRIAC, driver per motori a

passi, ecc. |

Ovviamente non è possibile utilizzare gli I/O programmati a

livello 0 come ingressi, ovvero i contatti non potranno essere collegati tra il

pin e la Vcc, cercando di rilevare l'azionamento con un livello alto. In tal

caso si corticuiterebbe il MOSFET N alla Vcc, danneggiandolo.

La caratteristica del quasi-biderezionale consente di utilizzare

il PCF8574 per espandere sia uscite che i ingressi con un solo componente ed in

modo molto flessibile.

Ad esempio, nella gestione di una logica esterna bidirezionale,

come possono essere le linee dati di un modulo LCD, non occorre invertire la

direzione degli I/O per passare da uscita a ingresso: basta che in lettura i pin

siano impostati a livello alto.

Inoltre, la "mancanza" di registri interni rende estremamente

semplice la gestione del chip, che richiede solamente la sequenza indirizzo+dato.

Altre informazioni.

Per informazioni dettagliate su segnali, temporizzazioni, ecc.

si rimanda ai fogli dati.

Può essere utile sapere che:

-

CAT9554/A

di OnSemi è analogo a PCF8574, con la possibilità di lavorare anche

su bus a 400kHz

-

JLC1565B

di OnSemi è similare, ma contiene anche un DAC a 6 bit

-

esiste un PCF8575

a 16 bit.

Documentazione.

e inoltre:

|