LCD controller.

HT1621 è un controller per LCD a 128 punti (32x4) prodotto dalla

taiwanese Holtek.

I caratteri presentati sul pannello LCD sono mappati in memoria RAM. La configurazione

software del controller lo rende adatto a molteplici applicazioni.

Le caratteristiche essenziali sono:

- Oscillatore RC integrato 256kHz

- Ingresso esterno per cristallo da 32,768 kHz o sorgente di frequenza a 256 kHz

- Selezione di un bias a 1/2 o 1/3 e selezione LCD a 1/2 o 1/3 o 1/4.

- Comando per buzzer piezo con frequenze selezionabili (2kHz/4kHz)

- Comando di spegnimento per ridurre il consumo energetico

- Generatore di base del tempo incorporato e WDT con uscita esterna

- 8 configurazioni timer e WDT

- Interfaccia seriale a 3-4 fili

La famiglia HT162x comprende 7 diversi modelli, con diverse

possibilità di comando dei segmenti, da 32 a 64.

Il chip è disponibile i package SSOP a 48 pin o LQFP-A a 44 o 48 pin.

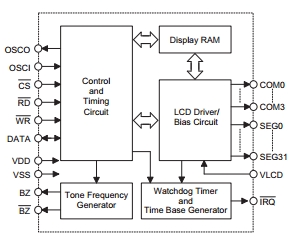

Il diagramma logico è il seguente:

|

- CS - chip

selection

- BZ, BZ-

tone output

- WR,RD,DATA

- linee di comunicazione

- COM0-3, SEG0-31 - uscite per LCD

- IRQ - time

base o WDT output

|

Nei dettagli:

| Label |

Pin |

Descrizione |

| CS |

1 |

Ingresso selezione chip con pull-up

Quando il CS è a

livello alto, l'accesso a HT1621 è disabilitato. Viene azzerato anche il circuito dell' interfaccia seriale.

Se CS è a livello basso,

è abilitata la comuniacazione sull'interfaccia seriale. |

| RD |

2 |

E' l'ingresso del clock di lettura, con pull-up.

I dati sono emessi dalla RAM di HT1621 alla linea DATA sul fronte di

discesa del clock. Il controllore host può utilizzare il bordo ascendente successivo per bloccare i dati

in uscita. |

| WR |

3 |

E' l'ingresso del clock di scrittura, con pull-up.

I dati scritti sono trasferiti all'HT1621 sul fronte di salita del

clock. |

| DATA |

4 |

Ingresso/uscita dati (bi direzionale) |

| Vss |

5 |

alimentazione negativa |

| OSCI |

7 |

I pin sono collegabili ad un cristallo esterno a 32.768kHz per

generare un orologio di sistema, oppure ad una sorgente esterna da

256kHz (collegata a OSCI). Se è selezionato un oscillatore RC

onchip, i

pin OSCI e OSCO possono essere lasciati aperti. |

| OSCO |

6

|

| VLCD |

8

|

Alimentazione pannello LCD |

| Vdd |

9

|

Alimentazione positiva 2.4-5.2V |

| IRQ |

10

|

Uscita open drain per tempo o WDT |

BZ

BZ |

11

12

|

2/4kHz output tone |

| COM0-3 |

13-16

|

LCD common out |

| SEG0-31 |

48-17

|

LCD segments out |

Il foglio dati riporta le caratteristiche elettriche ed i

relativi parametri.

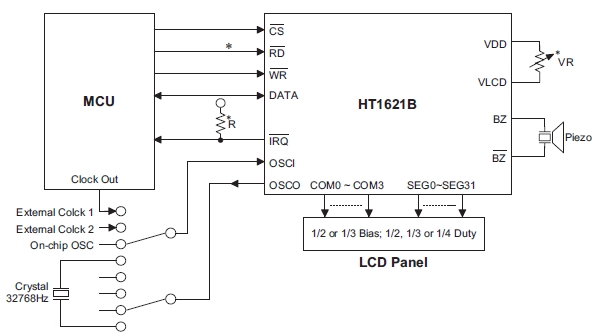

L'interfaccia tipica con un microcontroller host:

Il clock può avere tre sorgenti: un segnale esterno a 256kHz,

un quarzo a 32768Hz o l'oscillatore interno.

La linea RD può essere opzionale

se non è richiesta la lettura di dati dal controller.

La linea IRQ può essere

opzionale: invia un segnale relativo ad un tempo impostato nel controller o all'overflow

del WDT.

La linea VLCD va collegata con la Vdd attraverso una resistenza per regolare il

contrasto. Indicativamente, con Vdd=5V, VLCD dovrà essere 4V e VR circa

15-20kohm.

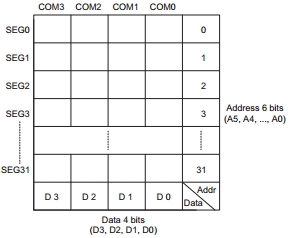

La memoria RAM.

|

La memoria di visualizzazione statica (RAM) è organizzata in 32x4 e memorizza i dati visualizzati.

Il contenuto della RAM è direttamente mappato nel contenuto del display LCD.

I dati nella RAM sono accessibili :

- in scrittura

- in lettura

- in

modalità READ-MODIFY-WRITE.

|

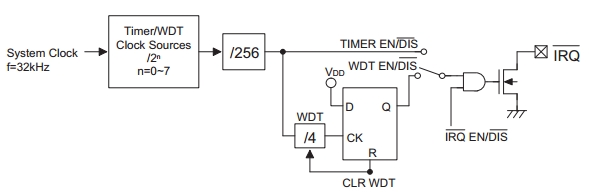

Il clock di sistema viene utilizzato per generare il time base/Watchdog Timer

(WDT) e per comandare la scansione dell' LCD. La fonte del clock può essere un oscillatore on-chip RC (256kHz),

un oscillatore a cristallo (32.768kHz) esterno, oppure una sorgente di clock

esterna a 256kHz, selezionabili da software.

dell' orologio mediante l' impostazione S/W. Il clock interno RC è

impostato per default all'accensione.

Nel caso di oscillatore RC onchip o oscillatore a cristallo, la

modalità spegnimento ridurrà il consumo energetico.

All'accensione il controller è disabilitato, condizione di

minimo consumo: il clock di sistema è arrestato e il

generatore bias dell' LCD è spento. Questa condizione è ottenibile anche con

il comando SYS_DIS (disponibile solo per l' oscillatore RC

on chip o per il cristallo).

Una volta che l' orologio di sistema si arresta, il display LCD diventa vuoto e la base del

tempo/WDT perde la sua funzione.

Il comando SYS_EN avvia il clock e il bias del display.

WDT/Timer.

Il generatore di base del tempo è composto da un ripple counter

a 8 stadi è progettato per generare una

base precisa di tempi. Il watchdog (WDT) è composto da un generatore di base a 8

stadi, insieme ad un contatore a 2 stadi, ed è progettato per interrompere il controllore host o altri sottosistemi

nel caso di stati anomali o indesiderati, errori di esecuzione, ecc.

Il flag del timer o del WDT possono essere collegati

alternativamente all' uscita IRQ, in mod programmabile. Il pin IRQ di

uscita è open drain.

Ci sono complessivamente otto sorgenti di frequenza disponibili per il generatore di base

tempi e il WDT. La frequenza viene calcolata con la seguente equazione fWDT = 32kHz / 2n

dove il valore di n è compreso tra 0 e 7.

Il WDT condivide lo stesso contatore a 8 stadi. Così, il comando

WDT DIS disabilita il watchdog, mentre

il comando WDT EN lo abilita e collega al WDT il pin di di segnalazione IRQ

time-out .

Il WDT può essere cancellato eseguendo il comando CLR WDT. Il contenuto del

timer viene cancellato eseguendo il comando CLR_TIMER. Il CLR WDT o il

CLR TIMER deve essere eseguito prima del WDT_EN o di TIMER_EN per cancellare il contenuto dei contatori.

Anche prima dell' esecuzione del comando IRQ_EN deve essere inviato un comando

CLR_ WDT o CLR_TIMER per evitare interrupt inaspettati.

Una volta scattato il time-out di WDT, il pin IRQ rimarrà ad una logica bassa fino a quando non viene emesso il comando

CLR_WDT o IRQ_DIS. IRQ_EN collega l'uscita del generatore della base tempi o del time-out WDT sul pin IRQ.

L' uscita IRQ può essere abilitata o disabilitata eseguendo l' esecuzione di IRQ_ EN o

IRQ_DIS, rispettivamente.

Dopo che l' uscita IRQ è disabilitata, il pin IRQ

rimarrà allo stato flottante: è un open drain e richiede un pull-up.

Il generatore di tono.

Il generatore di tono può emettere un segnale di pilotaggio differenziale

BZ e BZ, che vengono utilizzati per generare

un tono singolo, su un buzzer piezoelettrico.

I comandi TONE_4K e TONE_2K servono ad impostare la frequenza di tono rispettivamente a 4kHz e 2kHz.

L' uscita del tono può essere attivata o disattivata con il comando TONE_ON o il comando

TONE_OFF.

Se il chip è disabilitato o l'emissione del tono è inibita, le uscite BZ rimarranno a basso livello.

Comando dell'LCD.

Di seguito, la tabella dei comandi disponibili, organizzati su

12 o 13 bit, di cui i primi tre sono l'ID:

| Nome |

ID |

Codifica |

D/C |

Funzione |

Def. |

| READ |

110 |

A5A4A3A2A1A0D0D1D2D3 |

D |

Read data from RAM |

|

| WRITE |

101 |

A5A4A3A2A1A0D0D1D2D3 |

D |

Write data to RAM |

|

| R-M-W |

101 |

A5A4A3A2A1A0D0D1D2D3 |

D |

Read and write RAM |

|

| SYS_DIS |

100

|

0000-0000-X |

C |

Turn system off |

* |

| SYS_EN |

0000-0001-X |

C |

Turn system on |

|

| LCD_OFF |

0000-0010-X |

C |

Turn off bias generator |

* |

| LCD_ON |

0000-0011-X |

C |

Turn on bias generator |

|

| TIMER_DIS |

0000-0100-X |

C |

Disable timer |

|

| WDT_DIS |

0000-0101-X |

C |

Eisable WDT |

|

| TIMER_EN |

0000-0110-X |

C |

Enable timer |

|

| WDT_EN |

0000-0111-X |

C |

Enable WDT |

|

| TONE_OFF |

0000-1000-X |

C |

Tone off |

* |

| TONE_ON |

0000-1001-X |

C |

Tone on |

|

| CLR_TIMER |

0000-11XX-X |

C |

Clear timer |

|

| CLR_WDT |

0000-111X-X |

C |

Clear WDT |

|

| XTAL_32K |

0001-01XX-X |

C |

Crystal oscillator |

|

| RC_256K |

0001-10XX-X |

C |

Internal RC oscillator |

* |

| EXT_256K |

0001-11XX-X |

C |

External clock |

|

| BIAS_1/2 |

0010-abX0-X |

C |

-

LCD 1/2 bias option

-

ab=00: 2 commons

option

-

ab=01: 3 commons

option

- ab=10: 4 commons option

|

|

| BIAS_1/3 |

0010-abX1-X |

C |

-

LCD 1/3 bias option

-

ab=00: 2 commons

option

-

ab=01: 3 commons

option

- ab=10: 4 commons option

|

|

| TONE_4K |

010X-XXXX-X |

C |

Tone frequency 4kHz |

|

| TONE_2K |

011X-XXXX-X |

C |

Tone frequency 2kHz |

|

| IRQ_DIS |

100X-0XXX-X |

C |

Disable IRQ |

* |

| IRQ_EN |

100X-1XXX-X |

C |

Enable IRQ |

|

| F1 |

101X-X000-X |

C |

Time base/WDT clock

output:1Hz

The WDT time-out flag after: 4s |

|

| F2 |

101X-X001-X |

C |

Time base/WDT clock

output:2Hz

The WDT time-out flag after: 2s |

|

| F4 |

101X-X010-X |

C |

Time base/WDT clock

output:4Hz

The WDT time-out flag after: 1s |

|

| F8 |

101X-X011-X |

C |

Time base/WDT clock

output:8Hz

The WDT time-out flag after: 1/2s |

|

| F16 |

101X-X100-X |

C |

Time base/WDT clock

output:16Hz

The WDT time-out flag after: 1/4s |

|

| F32 |

101X-X101-X |

C |

Time base/WDT clock

output:32Hz

The WDT time-out flag after: 1/8s |

|

| F64 |

101X-X110-X |

C |

Time base/WDT clock

output:64Hz

The WDT time-out flag after: 1/16s |

|

| F128 |

101X-X111-X |

C |

Time base/WDT clock

output:128Hz

The WDT time-out flag after: 1/32s |

* |

| TEST |

1110-0000-X |

C |

Test mode, user don't use |

|

| NORMAL |

1110-0011-X |

C |

Normal mode |

* |

Osservare che alcune condizioni sono default

all'accensione.

La seguente tabella raccoglie i comandi relativi al display, i cui primi 3

bit sono 100.

| Nome |

Codice |

Funzione |

| LCD_OFF |

1 0 0 0

0 0 0 0 0 1 0 X |

LCD spento |

| LCD_ON |

1 0 0 0

0 0 0 0 0 1 1 X |

LCD acceso |

| BIAS & COM |

1 0 0 0

0 1 0 a b X c X |

-

c=0 : 1/2 bias

option

-

c=1 : 1/3 bias

option

-

ab=00: 2 commons option

-

ab=01: 3 commons option

- ab=10: 4 commons option

|

Se sono stati emessi comandi successivi, l' ID del modo comando, tranne che per il primo,

verrà omesso.

l comando LCD_ OFF spegne il display disattivando il bias.

Il comando LCD_ ON, invece, attiva il display LCD.

BIAS e COM sono i comandi del pannello LCD. utilizzando le opzioni corrette, HT1621

può essere compatibile con molti tipi di pannelli LCD.

I comandi di lettura e scrittura sono raccolti nella seguente

tabella:

| Operazione |

Modo |

ID |

| Read |

Data |

110 |

| Write |

Data |

101 |

| Read-Modify-Write |

Data |

101 |

| Command |

Command |

100 |

Ci sono due comandi di modalità per configurare le risorse HT1621

e per trasferire i dati del display LCD. La configurazione HT1621 è chiamata modo

comando e il suo ID è 100.

Il modo comando consiste in un comando di configurazione del sistema, un comando di selezione della frequenza, un comando di configurazione LCD,

un comando di selezione della frequenza di tono, per timer/WDT e un comando di funzionamento.

I dati, invece, includono tre modalità: READ, WRITE, e

READ-MODIFY-WRITE

Il comando di modalità deve essere emesso prima dei dati. Se si inviano comandi successivi senza modificare

CS, non occorre

inviare che il primo ID e per i comandi seguenti può essere omesso.

Mentre il sistema è in funzione se

il pin CS dovesse essere impostato su 1, la modalità di funzionamento precedente verrà azzerata. Una volta

che il CS ritorna a 0, un nuovo ID deve essere inviato.

La comunicazione

Una completa interfaccia di comunicazione richiede cinque linee:

CS, RD. WR, DATA, IRQ.

La linea CS viene utilizzata per inizializzare l' interfaccia seriale

e per terminare la comunicazione tra

il controllore e l' HT1621. Se il pin CS è impostato su 1, i dati o i comandi emessi tra il controllore host

e l' HT1621 vengono ignorati.

La linea DATA è la linea seriale di ingresso/uscita dati. I dati da leggere o scrivere o i comandi da

inviare passano su questa linea, che deve essere bidirezionale.

La linea RD è il

clock che va fornito per leggere dati dall'HT1621. I dati sono clockati sul

fronte di discesa del segnale: l' host legge in dati corretti durante l' intervallo tra

il fronte in salita e quello discendente successivo dell' RD.

La linea WR è l' ingresso del clock

di scrittura. I dati, indirizzi o comandi sulla linea DATA sono tutti sincronizzati

sul fronte ascendente del segnale WR.

La linea IRQ è di

uso opzionale come interfaccia tra il controllore e l' HT1621. Il pin IRQ può essere

selezionato come uscita timer o uscita segnalatore di overflow WDT.

Nella pratica, se non usata, la linea IRQ

può essere omessa.

Così pure se non si prevede necessari la lettura di dati dall'HT1621, anche la

linea RD può essere

omessa, riducendo così l'interfaccia a soli tre fili.

Note.

-

HT1621 non dispone di una decodifica tra dato e segmenti, per cui i bit inviati a 1

corrispondono a segmenti accesi, quelli a 0 corrispondono a segmenti spenti.

Occorre utilizzare una semplice lookup table esterna per convertire i simboli

che si intendono presentare nella

corrispondente maschera di bit da visualizzare.

-

All'accensione il display è spento (condizione a basso consumo), ma i

registri non sono azzerati e possono contenere valori casuali.

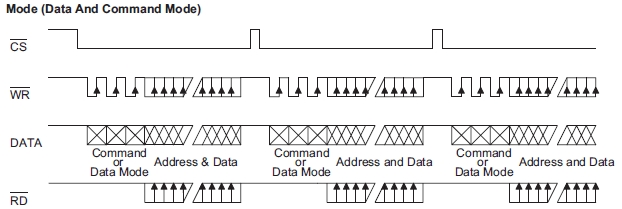

La gestione dei registri.

La gestione dei registri comporta una semplice struttura comando/dato.

Vediamo i diagrammi delle varie possibilità:

Trasmissione di comandi: Più comandi possono essere concatenati, inviando l'ID

100 solo per il primo.

CS va basso all'inizio della trasmissione e viene riportato a livello alto alla

fine.

I dati sono latchati sul fronte di salita del clock.

Un comando + dato: una coppia comando / dato viene inviata previo livello

basso sul CS. Dopo ogni coppia, il CS viene riportato a livello alto.

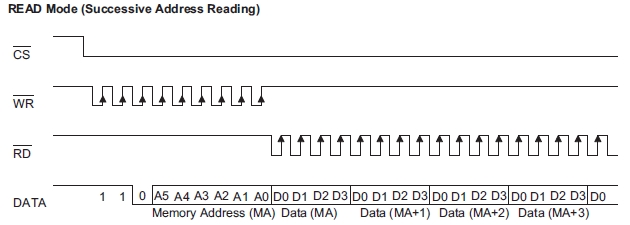

Un comando di lettura: la lettura utilizza il WR per inviare

l'indirizzo, mentre RD serve alla lettura dei dati.

Più letture successive: una serie di dati può essere letta di

seguito inviando l'indirizzo di inizio. Ogni 4 bit l'indirizzo viene

incrementato automaticamente. CS a livello alto termina la sequenza.

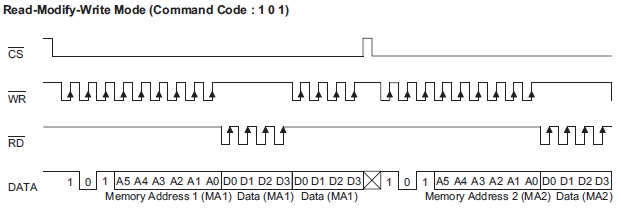

Modalità

R-M-W: il dato all'indirizzo specificato viene letto e immediatamente riscritto.

Ogni azione è limitata dal CS.

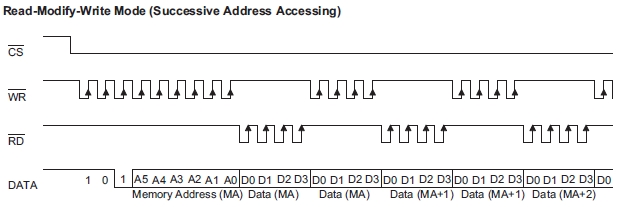

Modalità

R-M-W con azioni successive: si possono concatenare successive operazioni R-M-W

con 'indirizzo auto incrementante.

Scrittura:

un indirizzo e un dato sono legati nello stessa azione, che è terminata con CS

a livello alto.

Scritture

successive: più scritture successive sono concatenate con l'auto incremento

dell'indirizzo di partenza.

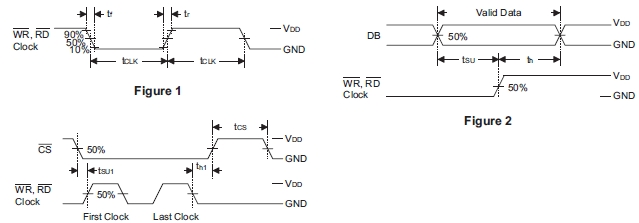

Timing.

| Nome |

Parametro |

min. |

max. |

Note |

| fCLK1 |

Serial Data Clock (WR pin) |

- |

150khz |

3V duty 50% |

| 300kHz |

5V duty 50% |

| fCLK2 |

Serial Data Clock (RD pin) |

- |

75kHz |

3V duty 50% |

| 150kHz |

5V duty 50% |

| tCLK |

WR, RD Input Pulse Width |

3.34us |

- |

3V write |

| 6.67us |

- |

3V read |

| 1.67us |

- |

5V write |

| 3.34us |

- |

3V read |

| tCS |

Serial Interface Reset PulseWidth |

250ns typ. |

|

| tsu |

Setup Time for DATA to WR, RD Clock Width |

120ns typ. |

|

| th |

Hold Time for DATA to WR, RDClock Width |

120ns typ. |

|

| tsu1 |

Setup Time for CS to WR, RDClock Width |

100ns typ. |

|

| th1 |

Hold Time for CS to WR, RDClock Width |

100ns typ. |

|

Non si tratta, quindi, di una periferica particolarmente veloce.

In particolare, va notato che l'alimentazione a tensioni minori di 5V

necessitano di temporizzazioni più lunghe.

Da notare anche che il clock in lettura deve essere minore di quello in scrittura.

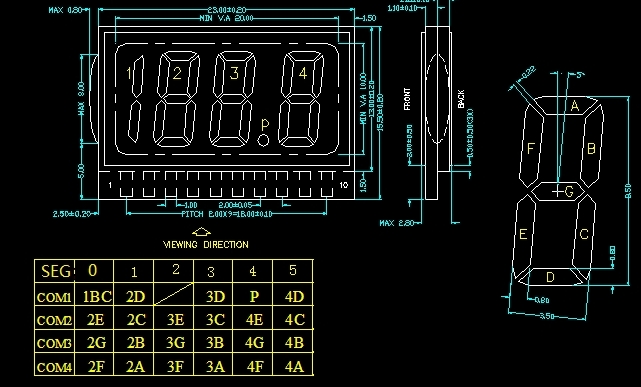

I moduli commerciali. Sono

facilmente reperibili in commercio almeno due tipologie di moduli LCD a sette

segmenti: con 6 cifre o con 3 cifre e mezza.

|

Questo modello dispone di retro illuminazione che può essere scelta

in diversi colori.

Ci sono 6 cifre a 7 segmenti da 2.4", di cui 3 con punto decimale,

più una barra di stato con il simbolo di una batteria.

La tensione di alimentazione può variare tra 4.7 e 5.2V con una

corrente dichiarata di 4mA. |

Per questo modello, la mappa dei segmenti è la seguente:

Ne

risulta che la corrispondenza tra bit e segmenti è questa:

| |

Seg. pari |

Seg. dispari |

| COM |

D0 |

D1 |

D |

D3 |

D0 |

D1 |

D2 |

D3 |

| segmento |

dp |

c |

b |

a |

d |

e |

g |

f |

Questo richiede una opportuna lookup table di decodifica da

valore a maschera dei segmenti.

Il bit iniziale comanda il punto decimale in tre indirizzi e i

segmenti dell'indicatore di batteria negli altri 3. Un

altro modulo comune è questo:

|

Dispone di 3 cifre e mezza, con un punto decimale e retro

illuminazione solitamente blu.

La tensione di alimentazione può variare tra 4.3 e 5V.

Il consumo dichiarato è 2mA. |

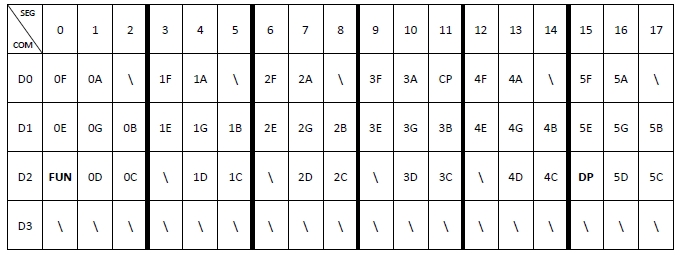

La mappa dei segmenti è questa:

Un ulteriore modello commerciale dispone sempre di 6 cifre:

|

L'altezza dei caratteri è1.4". Oltre alle 6 cifre, sono

accessibili un punto decimale, un doppio punto centrale e il simbolo di

una clessidra. |

La mappa dei segmenti è questa:

DP

è il punto decimale

CP sono i doppi punti stile orologio

FUN è il simbolo della clessidra. Esistono varie altre

realizzazioni con LCD diversi e controller della famiglia HT1621, oltre a

numerose applicazioni con LCD custom.

DRIVER.

Sul WEB sono disponibili vari esempi di librerie in C.

Per quanto riguarda l'Assembly, è stato realizzato un driverper il modello

688750. Qui trovate una versione

per Enhanced Midrange.

Documentazione.

|