|

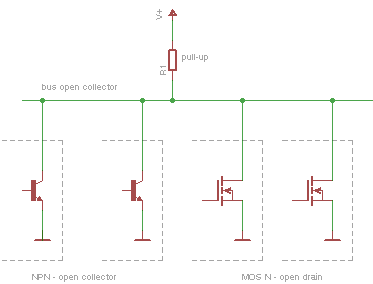

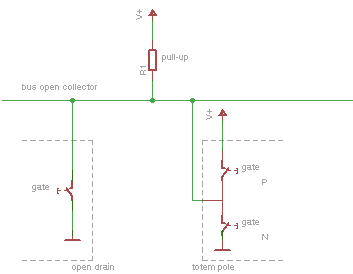

Una configurazione comune che permette una trasmissione di dati seriali su

una sola linea fisica è quella detta open collector.

|

Come dice il nome, vari dispositivi sono

"appesi" alla linea del bus attraverso transistor NPN in

configurazione a collettore aperto (open collector) o con transistor

MOSFET nell' equivalente open drain.

Su una stessa linea possono essere collegati teoricamente un numero

illimitato di dispositivi.

La linea è mantenuta a livello alto da una resistenza di pull-up.

Questa, per migliorare le prestazioni in velocità di commutazione

potrà essere sostituita con vantaggio da un generatore di corrente. |

Poiché la resistenza di pull-up è esterna ai dispositivi, dal punto di

vista teorico non è necessario che la V+ sia quella di alimentazione dei chip:

basta che non sia superiore alla tensione commutabile da parte degli switches.

In generale, però si tenderà ad utilizzare spesso proprio la tensione di

alimentazione (Vdd) dei semiconduttori, per ragioni di comodità, dato che, ad

esempio, in un microcontroller si utilizzeranno i GPIO interni configurabili

come open drain.

Comunque è anche diffuso l' impiego di tensioni più elevate dei classici 5V,

quando gli switches possono commutare queste tensioni, ad esempio 12 V. Un altro vantaggio

di questa configurazione è che, essendo la corrente sul bus indipendente dal

numero delle unità collegate, per inserirne una nuova basterà semplicemente

"appenderla" al bus. I semiconduttori sono utilizzati

essenzialmente come interruttori che passano dal blocco completo alla

saturazione.

|

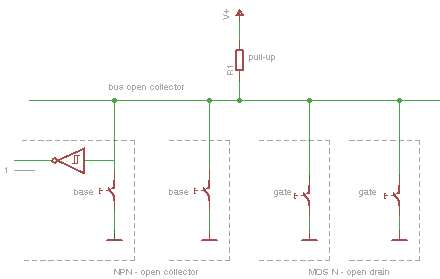

Le unità trasmittenti sono dotate dei transistor-switch che,

chiusi, mandano a livello basso la linea.

Però ogni unità potrà avere anche un gate di ricezione: la sua presenza, essendo un ingresso ad elevata impedenza, non

influenza lo stato impostato sul bus dagli switches o dal pull-up.

Si tratta quindi di un sistema di trasmissione e ricezione su una

unica linea fisica. |

Sappiamo che le cifre del sistema binario sono solo due : 0 e 1 e che esse

corrispondono, nel circuito elettrico equivalente, a due livelli di tensione

ben determinati:

| 0 |

1 |

| basso |

alto |

| Gnd |

Vcc |

| Vss |

Vdd |

In effetti, per motivi costruttivi, si avrà questa equivalenza:

| 0 |

1 |

| "quasi" Gnd |

"quasi" Vcc |

che, in forma grafica, possiamo rappresentare così:

|

- VIL — la massima tensione su un pin di ingresso che

verrà letta come un basso logico.

- VIH — la minima tensione su un pin di ingresso che

verrà letta come un alto logico.

- Forbidden region — la regione "indeterminata" tra il

livello di tensione VIL e VIH.

Tensioni di

ingresso in questo intervallo possono essere lette come basse o alte a

seconda di fattori casuali e costruttivi.

Come ingresso di un sistema

logico è ovvio che un livello produrrà un risultato piuttosto che il

livello opposto; quindi, è fondamentale che gli ingressi del circuito

logico siano ben determinati nel loro valore. |

Allo scopo di determinare una uscita precisa del ricevitore, esso sarà

possibilmente a Trigger di Schmitt per ripulire il segnale da incertezze e

disturbi.

Una particolarità di questa configurazione è che non esiste, tra le

varie unità trasmittenti, la possibilità di conflitto che determini problemi

fisici al bus.

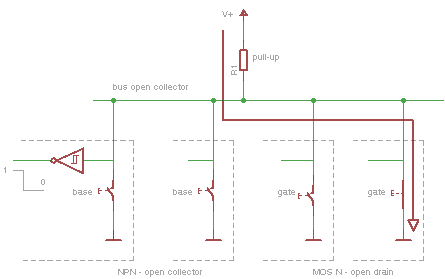

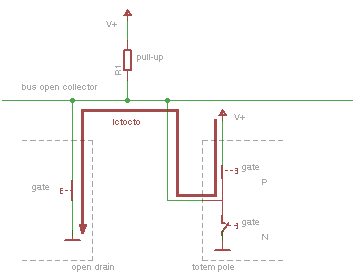

Come abbiamo visto nello schema precedente, se nessuno degli switches a

semiconduttore è chiuso, nel bus non passa altro che la minima corrente di

perdita delle giunzioni e la resistenza del pull-up mantiene il bus a livello

alto.

|

Se un semiconduttore è portato in saturazione,

costituisce un collegamento a bassissima resistenza verso la massa.

Attraverso di esso passa una corrente limitata dalla resistenza del

pull-up:

Id = V / R1

I ricevitori sul bus individueranno la variazione di

tensione e la riporteranno alle loro uscite.

Quindi, aprendo e chiudendo gli switches, potrò inviare

sequenze di bit 1 e 0. |

Ogni unità ricevente avrà a disposizione questi dati, così ottenuti:

- il bus sarà a livello 0 quando uno switch andrà in conduzione. Il

livello 0 è ottenuto dallo switch che chiude verso massa.

- il bus sarà a livello 1 quando nessuno switch è in conduzione. Il

livello 1 è garantito dal pull-up

A seconda dello stato dei gate di comando degli switches e della polarità

dei ricevitore, si potrà parlare di configurazioni "wired AND"

(a logica

positiva) o "wired OR" (logica negativa). Una "wired AND" si comporta come

l' AND booleano di due (o più) porte. Una "wired OR" Si comporta come il booleano OR

per la logica negativa.

Normalmente si fa riferimento ad una logica positiva, ovvero:

- Se solo una porta ha l’uscita bassa (FALSE), la linea va a massa e l’uscita è bassa (FALSE).

- Per ottenere un’uscita alta (TRUE), tutte le porte devono avere uscita alta (TRUE).

Nel nostro caso, l' uscita bassa equivale allo switch chiuso e l' uscita

alto allo switch aperto (livello alto imposto dal pull-up).

Può però determinarsi un caso particolare.

|

Per qualche ragione, più di uno switch va in

conduzione.

Il risultato è che la corrente nel bus NON può in ogni caso

superare il valore di:

Id= V / R1

dato che è limitata dal pull-up.

Quindi, anche quando, per errore, due o più unità vadano in conduzione allo

stesso tempo, non si verifica alcuna condizione di sovra corrente.

La corrente Id si ripartirà sui vari switches in conduzione. |

Ovviamente, se questo non rappresenta alcun pericolo per il bus e per le

unità collegate, il concorrere di più unità sul bus danneggia il dato

trasmesso: se l' unità che in quel momento sta trasmettendo un livello 1 (bus

rilasciato) si trova ad avere in parallelo un' altra unità che cerca di

trasmettere uno 0, il bus andrà a livello basso e il dato a 1 sarà danneggiato.

Si dice che è un bus con la priorità al livello basso. Quindi

occorrerà che siano introdotti sistemi di sicurezza prima che un dispositivo

inizi a trasmettere. Ad esempio, il trasmettitore che vuole

inserirsi sul bus, dovrà verificare che linea sia a livello alto per un certo

periodo prima di iniziare; e da parte dell' unità che sta trasmettendo

occorrerà verificare che i suoi dati a 1 siano effettivamente tali sul bus.

In caso di errore sarà necessario implementare qualche sistema di recovery.

Queste situazioni di collisione accadono in sistemi in cui siano possibili

più unità trasmittenti sul bus (multi-Master), come ad esempio I2C,

dove esistono simili verifiche. I bus open collector, per la loro

semplicità costruttiva e di gestione, sono abbastanza diffusi.

Appartengono a questo genere di struttura:

- I2C

- SMBus

- Access.Bus

- PS/2 (tastiera e mouse dei PC)

- LIN

- M-Bus

- vari bus per domotica

- One-Wire

Microcontroller e bus open collector

E' veramente opportuno considerare che la grande diffusione dei

microcontroller embedded per impieghi generici fa si che con essi si realizzi

una enorme quantità di applicazioni.

Tra queste sono presenti anche le comunicazioni seriali su bus diversi

(RS-232, 485, SPI, I2C, USB, CAN, LIN, ecc.). In genere, i microcontroller

più recenti e di fascia medio-alta dispongono di periferiche integrate che

consentono una gestione diretta di queste comunicazioni, con pin che si

adeguano alle specifiche dei vari sistemi. Resta però comunque la possibilità di realizzare accessi a questi bus e

protocolli attraverso tecniche di bit-banging, anche in microcontroller che

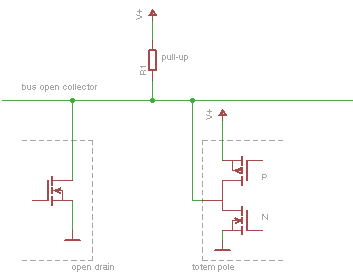

non dispongano dei moduli integrati. E spesso questi microcontroller non dispongono neppure dei pin adeguati a

comandare una linea open-collector. Se vari microcontroller hanno la

possibilità di programmare un GPIO come open drain, i PIC dispongono in

genreale di un

solo elemento open drain, tipicamente RA4, mentre tutti gli altri pin

sono dei totem-pole.

|

Un totem pole è composto da una coppia complementare

N-P. Questo offre due possibilità:

- quando è in conduzione l' elemento N, il pin è collegato a

massa.

- Quando è in conduzione l' elemento P, il pin è collegato alla

Vdd.

Se entrambi non sono in conduzione, il pin è ad alta impedenza.

Ovviamente non è ammesso che entrambi gli switches vadano in

conduzione contemporaneamente, dato che si genererebbe un corto

circuito tra Vdd e Vss. |

Per evitare questa situazione, la logica interna che comanda i gate dei due

MOSFET è organizzata in modo tale da impedirne la conduzione allo steso

istante. Ma non è possibile inserire questo genere di port in un bus open

collector senza particolari considerazioni. Infatti è presente un grave rischio:

|

Vediamo ora il diagramma precedente come un array di

interruttori e sarà semplice comprendere di cosa si tratta.

Se tutti gli interruttori sono aperti, il bus è appeso alla V+

attraverso il pull-up e nessuna corrente attraversa R1.

Questa situazione si può ottenere nei dispositivi open drain non

comandando il gate del MOSFET.

Nei dispositivi totem-pole, invece, se sono configurati come uscite,

avranno applicata alla logica di controllo un livello logico 1 o 0 a

seconda di quanto programmato nel registro del port. |

Ovvero il pin in uscita digitale potrà assumere esclusivamente un livello

pari alla Vdd o alla Vss: uno dei due MOSFET sarà chiuso e questo collegherà

il pin a una o all' altra delle barre di alimentazione.

E, ricordiamo, si cerca di fare in modo tale che la resistenza di conduzione

dei MOSFET sia la minore possibile. Se consideriamo il totem-pole come uscita programmata a

livello 0, sarà in conduzione il MOSFET N e il bus sarà tirato a

livello basso. Qualsiasi altro dispositivo open drain che porti pure a livello

basso il bus, non creerà alcun problema di corrente: si avrà una collisione

come visto in precedenza (la corrente dipende non dal numero degli switch

chiusi, ma dalla R1).

|

Se però abbiamo impostato il totem pole per uscita = 1,

si sarà chiuso il MOSFET P. Questo forza la Vdd a collegarsi direttamente al

bus, attraverso la minima resistenza di conduzione del MOSFET

stesso.

Se, per errore, entra in conduzione un' altra unità, il suo switch

chiude verso massa: si genera un corto circuito diretto tra la Vdd e

la massa attraverso:

Vdd - Mosfet P- bus - open drain - massa

E' chiaro che questa connessione sarà molto

probabilmente mortale per i dispositivi interessati, dato che la

corrente sarà limitata solo dalla resistenza degli switches, che, per

costruzione, è la più bassa possibile. |

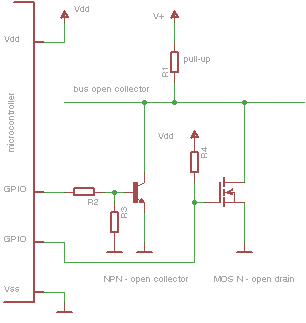

Non essendo i GPIO, configurati in modo di uscita

digitale, dotati di funzione di 3-state, l'unico modo per non avere uno dei due switch chiusi è quello di

programmare il pin come ingresso: in tal caso entrambi i MOSFET saranno

disattivati e al pin sarà presente solo il carico dovuto al gate di ingresso,

che ha impedenza elevata e quindi non influisce sulla tensione imposta dal

pull-up.

Dunque, volendo collegare un pin totem pole ad un bus open collector ci

potranno essere due via:

- aggiungere un semiconduttore esterno open drain - open collector

- utilizzare una manovra software

|

|

La prima soluzione è la più semplice, ma richiede l'

aggiunta di un paio di componenti esterni.

Per un transistor NPN occorrerà una resistenza di limitazione

della corrente di base (R2) e, opzionale, una resistenza di pull-down

(R3) per tenere il transistor interdetto nel caso di 3-state del GPIO.

Il MOSFET N dovrà essere un logic-gate. La R4 è un pull-up

per la conduzione del gate.

La logica è invertita: comandando a livello alto la

base/gate del transistor, esso va in conduzione e il livello del bus

va basso.

In questo modo è possibile comandare un bus o.c. con una

V+ diversa dalla Vdd. |

R2 potrà essere qualche k , dipendentemente dal guadagno del transistor

(1-10k). Serve a mandarlo in saturazione. R3, opzionale, terrà bloccato il

transistor con il GPIO impostato come input. Il tranistor è un comune NPN per

usi generali (BC357, 2N2222, ecc)

Per il MOSFET (su un bus a bassa corrente, sarà del genere VN2222, BS170 e

simili), R4 potrà essere 10-22k.

La seconda soluzione consiste in quanto segue:

- se vogliamo imporre un livello 0 al bus, programmiamo il pin come uscita

dopo aver programmato il registro del port a livello 0. Questo collegherà

il pin al bus con il MOSFET N chiuso e il P aperto

- se vogliamo applicare un livello 1 al bus, ovvero lasciare libero il bus

al livello imposto dal pull-up. programmeremo il pin come ingresso.

Questo disabilita i MOSFET di uscita e lascia collegato solo il gate di

ricezione; il pin si porta in stato di alta impedenza e R1 tira su (pull-up) la

tensione del bus.

Ad esempio, in Assembly per PIC Microchip:

; driver per pin di controllo su

o.c. bus

; pin RC1 a livello 0

out_0 MACRO

bcf

LATC,1 ;

preset del registro di uscita a 0

bcf

TRISC,1 ;

direzione pin in uscita

ENDM

; pin RC1 a livello 1

out_1 MACRO

bsf

TRISC,1 ;

direzione pin in ingresso

ENDM |

Inoltre, abbiamo citato un altro fatto molto importante: totem pole lavora

a livello della Vdd, tensione positiva che alimenta il chip.

La tensione V+

del bus può essere diversa dalla Vdd, ad esempio maggiore. Il suo limite è

dato solamente dalla tensione sopportabile dagli open drain - open collector

collegati.

Quindi ne risulta che il totem pole NON può essere collegato al bus open

collector se questo ha una tensione diversa da Vdd, non solo nel senso del

valore assoluto, ma anche della sorgente. Dunque, se, come abbiamo visto, è

possibile emulare da programma un collegamento con il bus open collector,

questo va fatto a ragion veduta e dopo aver chiare quale sono le implicazioni.

Il bus fisico

La struttura fisica del bus è determinante per la qualità dello scambio

di dati e presenta alcune problematiche.

In particolare, la connessione fisica risulta afflitta da una certa capacità

parassita dovuta all' esetensione dei conduttori e alle capacità proprie dei

dispositivi collegati. La capacità, assieme alla resistenza di pull-up,

costituisce una rete RC che si oppone alle variazioni di tensione dovute alle

commutazioni.

Ne risulta la necessità tipica di aumentare la corrente sul bus all'

aumentare della frequenza. Questo comporta un maggior consumo a frequenze

elevate.

Inoltre, la capacità dei cavi, solitamente superiore a 50-100 pF/m pone un

limite alla distanza che la connessione può coprire.

E, generale, maggiore è la distanza/capacità, minore sarà la frequenza

applicabile al bus.

Ovvero, se la velocità non è un limite, riducendo la frequenza si otterrà la

copertura di distanze maggiori. Per ovviare al rallentamento dei tempi di

salita e discesa dei segnali, può essere utile inserire al posto del pull-up

un generatore di corrente.

Ad esempio, ecco l' effetto positivo sulla forma d'onda dei segnali in un bus

I2C ottenuta inserendo l' integrato LT4311 di

Linear Technology.

Quanto maggiore sarà la lunghezza delle connessioni, tanto maggiori

saranno le probabilità di captare un disturbo. Probabilità che diventa

certezza quando il circuito è inserito in ambienti elettricamente

rumorosi,

con presenza di relè, elettromagneti, trasformatori, motori, ecc., sopratutto in montaggi

disordinati. In questi casi sono soluzioni comuni la schermatura dei cavi, il

twistaggio dei conduttori (segnale + massa), l' inserzione i bus exterder o

buffer e l' isolamento galvanico.

Quale valore per il pull-up ?

Ci si può porre il problema di quale valore scegliere per la R1 di pull-up

per il bus open collector.

In modo molto sintetico possiamo dire che il valore del pull-up

R1 deve essere in grado di portare a livello alto la tensione sul pin.

Questo dipende dalla corrente assorbita dal pin e dalla famiglia logica a cui

appartiene il dispositivo: da famiglia a famiglia i livelli accettati come

alto e basso variano.

|

Va considerato che il circuito equivalente dell' ingresso può

essere sintetizzato come una resistenza.

Quando il contatto è chiuso, il pin è collegato direttamente alla

massa attraverso la bassa resistenza del contatto stesso e del suo

cablaggio, per cui il livello è sicuramente basso.

Quando l' interruttore è aperto, il livello di tensione al pin è

quello stabilito dal partitore composto da R1 e dalla resistenza dell'

ingresso Rinput.

O, in altre parole, la caduta di tensione su R1 determinata dalla

corrente che affluisce al pin dalla Vcc (attraverso R1) deve essere

tale da non scendere al di sotto del livello "alto" per quel

dato dispositivo. |

Vanno fatte due considerazioni:

- Quando il contato è chiuso, attraverso R1 passa una

corrente data da Vcc / R1. Se il valore di R1 è basso, la

corrente sarà elevata e questo non è di alcuna utilità al circuito,

anzi, è condizione che si cerca di evitare nelle realizzazioni che

richiedono un basso consumo

- Quando l' interruttore è aperto, il valore di R1 e della

corrente assorbita dal pin Iin determina la tensione al pin

stesso data da R1 * Iin, oppure alla tensione derivata dal

partitore R1- Rinput. Se R1 ha un valore troppo alto,

la tensione al pin non arriverà al livello alto

Quindi, la prima condizione tende a cercare valori di R1 il più alto

possibile, mentre la seconda tende ad abbassarne il valore.

Dal punto di vista pratico, per il calcolo delle resistenze di pull-up per

i vari standard, è opportuno ricorre alle informazioni fornite dai

costruttori ed alle relative note applicative.

|