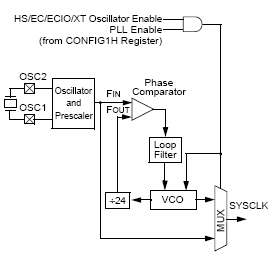

IL PLL

Alcune modalità di clock contengono PLL nella loro sigla e

indica la possibilità di utilizzare un sistema di

moltiplicazione del clock a Phase Locked Loop (PLL).

Questo speciale

circuito è previsto, ad esempio, per ottenere 40 MHz a partire da un ingresso di 10

MHz,

ovvero moltiplica per 4 la frequenza del quarzo.

Il clock in uscita è utilizzata per il core

del processore e per gli I/O che richiedono frequenze elevate, come ad

esempio l' interfaccia USB (48MHz / 4 = 12 MHz).

|

Il modo PLL è generalmente richiamabile con

- HSPLL

- XTPLL

- INTOSC1PLL

- INTOSC2PLL

- ECPLL

- ECIOPLL

ma i diversi chip possono avere più o meno opzioni. In

particolare i tipi dotati di USB hanno una struttura del clock molto

complessa, ad esempio con la disponibilità di post scaler per

derivare i clock interni dal PLL. Questo permette, ad esempio, al

processore alla porta USB di usare differenti valori di clock

derivati da un unica sorgente comune. (Il postscaler dei modi HT, HS

e EC può essere scelto solo tra 2, 3 , 4 e 6).

|

Con l' uso del PLL è necessario tener conto di alcune

avvertenze:

|

AVVERTENZ

E

:

-

Il PLL

è programmabile

come attività, ma non come valore, in quanto,

se inserito

ha un fattore di

moltiplicazione fisso uguale a 4.

Occorrerà che nei modi con

componenti esterni, il quarzo non superi il valore di 10MHz (4 x 10 =

40MHz) o comunque la frequenza massima prevista per quel chip (ved. più

avanti).

-

Inoltre possono esistere alcune limitazioni nell' uso del

PLL.

Ad esempio per la famiglia PIC18F4321, il clock derivato dall'

oscillatore interno prevede l' aggancio del PLL solamente se è

stata scelta la frequenza di 4 o 8 MHz (ottenendo così rispettivamente 16

o 32 MHz), ma non per gli altri valori di clock selezionabili con il

registro OSCCON.

-

Sempre per la famiglia PIC18F4321, nel caso di cristallo

esterno, la selezione è possibile solo avendo configurato FOSC3:0 di

CONFIG1H per il modo HSPLL

|

Le pagine delle caratteristiche elettriche danno altre

informazioni sul PLL, ad esempio la tabella relativa a PIC18F4321:

In particolare va notato che il tempo di stabilizzazione del

PLL è dato con un massimo di 2 ms (param. F12), ovvero, da quando viene

attivato a quando l' oscillazione si è stabilizzata, potrebbe trascorrere

questo intervallo di tempo.

Il param. F13 indica che il jitter (ovvero la stabilità)

del clock generato dal PLL può oscillare in un massimo del +/- 2 %.

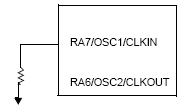

IL modo ER

Alcuni PIC dispongono di una modalità di oscillazione che

viene realizzata con il collegamento di una semplice resistenza al pin OSC1.

|

Questa resistenza è sostanzialmente messa a controllare la corrente di un

oscillatore RC interno; il suo valore, secondo il costruttore, può variare da

38 k a 1 Mohm, ottenendo frequenze tra 30 kHz e 4 MHz.

Il pin OSC2 (RA6) può essere programmato come uscita del clock / 4 oppure

come GPIO. |

ER è una modalità economica, ma non di precisione (time

insensitive application), dipendendo molto dalla tensione di alimentazione e

dalla temperatura. Per la resistenza sarà necessario utilizzare tipi a strato

metallico e non superare il Mohm in quanto, secondo i fogli dati, il circuito

diventa sensibile al rumore elettrico ed all' umidità.

Altre modalità

Alcuni PIC dispongono di una tecnologia a basso consumo,

denominata Nanowatt.

Alla base di questo sistema si trova un generatore di clock

interno, la cui frequenza di funzionamento può essere commutato da un

software.

Questo permette di ottimizzare il consumo di energia del PIC, variando la

frequenza di lavoro a seconda delle necessità.

La commutazione tra frequenze o sorgenti viene effettuata agendo su bit

di controllo di registri interni, durante il funzionamento. Questo consente,

diversamente dal modo SLEEP, di non arrestare completamente il processore, ma

di rallentarlo soltanto.

Va notato che il passaggio da una frequenza ad un' altra o da un oscillatore

ad un' altro richiede un certo tempo, dovuto alla necessità dell'

oscillatore di stabilizzarsi sul nuovo valore.

I fogli dati riportano queste temporizzazioni e alcuni flag nei registri di

controllo sono attivati dalla stabilizzazione degli oscillatori, permettendo

così un controllo della loro funzionalità.

Esiste anche la possibilità, in alcuni PIC, di gestire un

eventuale guasto dell' oscillatore primario, sostituendolo con uno di

"backup".

PIC con a bordo periferiche particolari, come l' USB,

hanno gestione del clock leggermente diversa, con le frequenze necessarie al

funzionamento della periferica.

In questi casi la consultazione dei fogli dati è sempre necessaria.