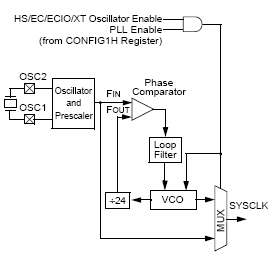

IL PLL

Alcune modalità di clock contengono PLL nella loro sigla e

questo indica la possibilità di utilizzare un sistema di

moltiplicazione del clock a Phase Locked Loop (PLL). Questo speciale

circuito è previsto per ottenere 40 MHz a partire da un ingresso di 10 MHz,

ovvero moltiplica per 4. La frequenza in uscita è utilizzata per il core

del processore e per gli I/O che richiedono frequenze elevate, come ad

esempio l' interfaccia USB.

|

Il modo PLL è generalmente richiamabile con

- HSPLL

- XTPLL

- INTOSC1PLL

- INTOSC2PLL

- ECPLL

- ECIOPLL

ma i diversi chip possono avere più o meno opzioni. In

particolare i tipi dotati di USB hanno una struttura del clock molto

complessa, ad esempio con la disponibilità di post scaler per

derivare i clock interni dal PLL. Questo permette, ad esempio, al

processore alla porta USB di usare differenti valori di clock

derivati da un unica sorgente comune. (Il postscaler dei modi HT, HS

e EC può essere scelto solo tra 2, 3 , 4 e 6).

|

Con l' uso del PLL è necessario tener conto di alcune

avvertenze:

|

AVVERTENZ

E

:

-

Il PLL

è programmabile

come attività, ma non come valore, in quanto,

se inserito

ha un fattore di

moltiplicazione fisso uguale a 4.

Occorrerà che nei modi con

componenti esterni, il quarzo non superi il valore di 10MHz (4 x 10 =

40MHz) o comunque la frequenza massima prevista per quel chip (ved. più

avanti).

-

Inoltre possono esistere alcune limitazioni nell' uso del

PLL.

Ad esempio per la famiglia PIC18F4321, il clock derivato dall'

oscillatore interno prevede l' aggancio del PLL solamente se è

stata scelta la frequenza di 4 o 8 MHz (ottenendo così rispettivamente 16

o 32 MHz), ma non per gli altri valori di clock selezionabili con il

registro OSCCON.

-

Sempre per la famiglia PIC18F4321, nel caso di cristallo

esterno, la selezione è possibile solo avendo configurato FOSC3:0 di

CONFIG1H per il modo HSPLL

|

Le pagine delle caratteristiche elettriche danno altre

informazioni sul PLL, in particolare la TABLE 26-7

In particolare va notato che il tempo di stabilizzazione del

PLL è dato con un massimo di 2 ms (param. F12), ovvero, da quando viene

attivato a quando l' oscillazione si è stabilizzata, potrebbe trascorrere

questo intervallo di tempo.

Il param. F13 indica che il jitter (ovvero la stabilità)

del clock generato dal PLL può oscillare in un massimo del +/- 2 %.

La Frequenza Massima

La frequenza massima di funzionamento dipende dal chip e dalla

tensione di alimentazione.

Con una tensione di funzionamento minore sarà ridotta anche

la corrente assorbibile dal chip e questo riduce verso l' alto l' estensione

della frequenza di funzionamento.

Per contro, con una frequenza minore ed una tensione minore si otterrà un

consumo minore di potenza.

Il costruttore fornisce un grafico come questo per

visualizzare l' area di operatività garantita:

Questo diagramma rappresenta la gamma della frequenza di

lavoro per un PIC della famiglia 18LF4321.

Si nota bene come la

massima frequenza garantita si abbassi sensibilmente con l' abbassarsi della

tensione di alimentazione (i modelli LF arrivano ad operare da 5.5 V ad un

minimo di soli 2 V): a 2 volt non viene certificata la possibilità

di lavorare con clock superiore a 4 MHz.

e solo la soglia di tensione di 4.2 V ripristina la possibilità di arrivare

ai 40 MHz.

|

Ne consegue che debba essere verificato che il clock scelto sia

adeguato alle condizioni di funzionamento.

|

Per PIC18F4321, la cui tensione di funzionamento deve essere

compresa tra 5.5 e 4.2V, è applicabile tutta la gamma di frequenze di

clock.

Da qui risulta più chiara la principale differenza tra i

chip con F e con LF nella sigla.

In particolare, Microchip consiglia di andare cauti con la

commutazione del divisore interno di INTOSC (bit IRCF di OSCCON) con

tensioni inferiori ai 3 volt in quanto, come abbiamo visto, non è detto che

la frequenza scelta sia adeguata alla tensione di alimentazione del

processore. Se si esce dai limiti indicati nelle tabelle del foglio dati il

funzionamento del sistema può essere instabile o problematico.

Prove pratiche hanno permesso di verificare che un

PIC18LF2321P a 3.3V di alimentazione e temperatura ambiente attorno ai 20 C

funziona regolarmente con un quarzo esterno da 10MHz sia in modalità HS che

HSPLL (40MHz), ma, secondo il foglio dati, è una condizione non regolare e

quindi non garantita dal costruttore.