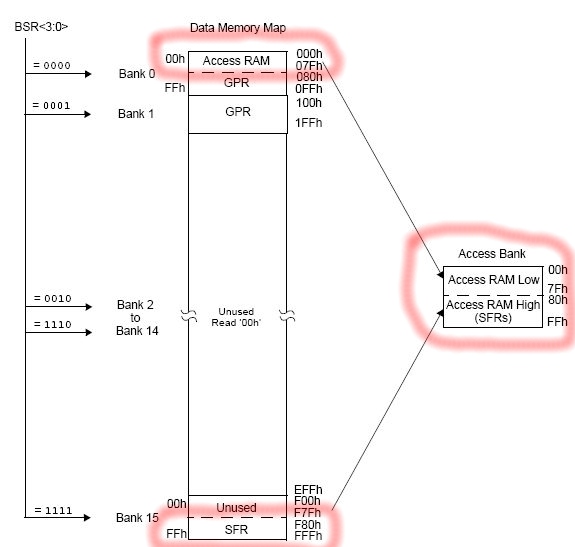

L' Access RAM

Per quanto visto sopra, se l' utente dei PIC si è

finalmente liberato del PCLATH e delle pagine della memoria programma, appare

ancora invischiato nel meccanismo a banchi della memoria dati. Però anche qui i

progettisti hanno cercato di porre rimedio. Se la soluzione del BSR e di movlb

rende già meno penosa la questione, molto importante è porre l' attenzione sul

banco 0 e sul banco 15 dello schema precedente : essi fanno parte di un meccanismo chiamato Access

RAM.

I suoi elementi essenziali sono questi :

-

a differenza dei PIC 16, i cui registri

speciali di controllo delle funzioni (SFR - Special Function Register) del

processore sono sparpagliati in più banchi, i PIC 18F hanno TUTTI i

registri speciali raccolti in un unico banco e per esattezza nella seconda

metà del banco 15, da F60h a FFFh. Questo permette di accedere a qualsiasi

registro speciale senza preoccuparsi di verificare in quale banco sta.

Questo è già un buon vantaggio.

-

I primi 96 bytes del banco 15, da F00h a F5Fh

non sono utilizzati, ma, sfruttando il meccanismo dell' Access RAM, vengono

"sostituiti" con la prima parte del banco 0, a formare un unico

banco, l' Access RAM, appunto, che così contiene nella metà bassa 96

registri general purpose, presi dal banco 0, e nella parte alta 160 bytes occupati dai registri

speciali.

Se torniamo allo schema della memoria possiamo evidenziare

la parte che ci interessa:

|

|

Questa è la mappa di memoria de PIC della famiglia 4321.

Il Banco 0 è suddiviso in due parti, la prima accessibile come ACCESS

RAM e la seconda con BSR = 0.

Segue un Banco1, accessibile con BSR = 1.

I rimanenti banchi da 2 a 14 non sono implementati ( scrittura ivi

diretta va persa e lettura sempre 0).

Il Banco15 è pure diviso in due : la prima metà non è implementata

(come i banchi precedenti), mentre nella seconda metà si trovano

raccolti gli SFR, raggiungibili con Access RAM. |

A cosa serve un tale accrocchio ?

Molto

semplicemente serve a questo:

-

attivando il bit di Access RAM (bit a negli

opcode che agiscono sulla memoria dati) il programmatore dispone immediatamente

di 96 bit di RAM e di tutti i registri del processore in un unico banco,

accessibile tra 00h e FFh, senza alcuna manovra addizionale sugli switches di

banco.

Questa quantità di memoria RAM può essere sufficiente per molte

applicazioni, mentre l' avere tutti i registri speciali in una sola area è

estremamente funzionale. In sostanza, considerando la singola pagina della

Memoria Programma e l' uso dell' Access RAM per la Memoria Dati, non è più

necessario prestare attenzione a pagine e banchi come era obbligo per i PIC16.

Inoltre, se nei PIC16 esisteva un' area di RAM comune a tutti i banchi di soli

16 bytes (70-7Fh), con l' Access RAM diventano disponibili 96 bytes senza

problemi di banco.

Ovviamente se il programma richiede una quantità maggiore

dei 96 bytes, sarà obbligo fare

uso dei bit di switch dei banchi BSR. In questo caso si abbandona l' Access RAM ,

ma l' area degli SFR e della prima metà del banco 0 sono comunque sempre

accessibili, questa volta però nella loro posizione naturale all' inizio ed

alla fine dell' area della Memoria Dati.

AVVERTENZA:

Altri

PIC18F, come la serie 2520-4520 hanno l'

Access RAM di diverse dimensioni, per cui, ad esempio, è composto da 128

bytes di RAM e 128 bytes di SFR.

Una consultazione del foglio dati del

componente usato permette di conoscere queste differenze.

|

Per ottenere il funzionamento BANKED è stato aggiunto un bit

speciale, il bit a, nell' opcode di diverse istruzioni: quando il suo

valore è a 1 si attiva l' Access RAM e i bit di

switch dei banchi (BSR) non hanno effetto, qualsiasi sia il loro valore; quando

è a 0 viene attivato il meccanismo del BSR e tutti i banchi disponibili sono accessibili a seconda del

valore dei BSR.

Nello stesso programma è possibile utilizzare a

piacere tanto l' Access RAM quanto i BSR. Nel passaggio da Access RAM a BSR e viceversa, il contenuto dei

registri non viene alterato.

La sintassi delle istruzioni che accedono alla

memoria dati sarà arricchita da questo switch a. Ad esempio, supponiamo di

voler muovere il valore contenuto nella locazione target

, in banco 0, al PORTA, che sta in banco 15.

movf target, w, a

; carica il valore di target

movwf PORTA, a ; sulla porta A |

L' utilizzo pratico non comporta alcun problema in

quanto MPASM, nelle ultime versioni, è sufficientemente intelligente da

decidere autonomamente cosa fare.

-

se la memoria richiesta è accessibile come Access RAM, il bit a sarà attivato

-

se la memoria richiesta non è raggiungibile

con l' Access RAM, MPASM userà i BSR

Quindi, nella pratica, il termine a della sintassi

non è necessario sia espresso, per cui :

movf target, w

; carica il valore di target

movwf PORTA ; sulla porta A |

andrà benissimo (almeno con MPASM). Da noatre che

in questa sintassi, MPASM intende la presenza dello switch a come indicatore

della volontà di usufruire dell' Access RAM.

Nel caso in cui si voglia utilizzare esplicitamente

i BSR, la forma sarà :

movf target, w,

banked ; carica il valore di target

movwf PORTA, banked ; sulla porta A |

il banked esprime

la volontà del programmatore di utilizzare i BSR.

Se la memoria richiesta non è raggiungibile con l'

Access RAM, MPASM utilizza BSR in ogni caso, ma occorrerà che i bit relativi

siano configurati nel modo corretto per raggiungere la destinazione richiesta.

Access RAM : da PIC16 a PIC18

L’ indirizzamento in

Acces RAM, è una delle più sensibili differenze tra i PIC16 e i PIC18.

Nei PIC16 i

registri speciali (SFR) erano distribuiti su tutti i banchi; di conseguenza, per

passare da uno all’ altro era necessario agire in continuazione su RP1:0.<

La necessità di prestare continua attenzione alla posizione dei registri

nei banchi rende noiosa la programmazione Assembler ed è fonte di facili errori

che poi sono difficili da sistemare. Certamente l’ Assembler mette a

disposizione il banksel che può essere anteposto a qualsiasi chiamata di SFR,

ma questo, se da una parte elimina gli errori di banco, dall’ altra

appesantisce drasticamente il listato.

Nei PIC18 non è più

necessario lavorare con la lista dei registi/banchi sotto gli occhi, perché

TUTTI i registri sono raccolti in un unico banco, per l’ esattezza la seconda

metà del Banco 15.

Ci si può domandare che vantaggio sia, se comunque occorre accedere ad un banco

per consultare gli SFR, ma è una domanda che ha una risposta inaspettata e

positiva: il meccanismo dell’ Access RAM. In cosa consiste ?

I progettisti di

Microchip hanno fatto si che un indicatore supplementare aggiunto all’

argomento delle istruzioni permetta di accedere direttamente alla prima metà

della RAM in Banco 0 e agli SFR, posti nella seconda metà del Banco 15, senza

alcuna altra formalità !!!

Sostanzialmente, il meccanismo unisce

la prima metà del Banco0 e la seconda metà del Banco15, creando l’ Access RAM. Dunque, scrivendo:

SetIO movf

setup1, w, A ; carica il valore di setup

movwf TRISB, A ;

della direzione di PORTB

movf

setup2, w, A ; carica valore setup2

movwf TRISC,

A ; della direzione di PORTC |

Si

potrebbe considerare una jattura il parametro a aggiuntivo, anche perché questo

vale per i banchi 0 e 15 e basta, ma ancora una volta MPASM lavora per noi e ci

permette di scrivere solo:

SetIO movf

setup1, w ; carica il valore di setup

movwf TRISB ;

della direzione di PORTB

movf

setup2, w ; carica valore setup2

movwf TRISC

; della direzione di PORTC |

riconoscendo le label dei registri nella loro

posizione in memoria e generando il codice corretto anche senza l’ aggiunta

della A !!

AVVERTENZA:

L' automatismo descritto vale per MPASM;

altri assemblatori potrebbero non disporne e quindi richiedere l’ aggiunta

della A.

In ogni caso, se il sorgente è passato a MPASM, che ci sia la A o

meno è indifferente, ma, per chiarezza di lettura, è opportuno farne a meno ed

utilizzare il suddetto automatismo.

|