Anche PORTB

è un registro a 8 bit per uso generico (GPIO - General Purpose IO) a

cui sono associate molte funzioni alternative.

In particolare PORTB supporta:

-

GPIO

-

funzioni analogiche

-

interrupt esterni

-

moduli CCP

-

ICSP-ICD

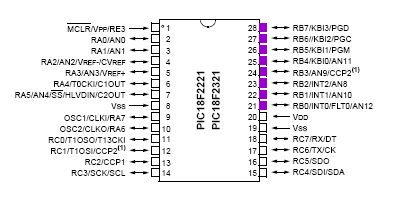

Nello schema di principio del controller, mettiamo in

evidenza il PORTB e i circuiti associati:

Fisicamente i pin si trovano qui:

|

Microchip mantiene un ragionevole senso nella disposizione delle

funzioni cercando di porle in modo successivo in corrispondenza dei

pin.

Va notato che RB7 e RB6 fanno parte del sistema di In Circuit

Debug (ICD) e In Circuit Serial Programming (ICSP) essendo:

- RB7 - PGD - dati

- RB6 - PGC - clock

|

Nei chip a 28 e 40 pin PORTB

è presente al completo con tutti gli 8 bit, da RB0 a RB7.

Dal punto di vista elettrico, la struttura dei PORTB è analoga a quella

vista per i PORTA.

Sono diverse le funzioni accessorie

programmabili oltre il GPIO. Tutti i pin hanno in uscita una coppia MOSFET

P/N e quindi sono in grado di azionare carichi sia alla Vdd che alla Vss (sink

e source).

La tabella seguente riporta il quadro completo di queste

possibilità. Da notare che, a seconda della funzione programmata, possono

esserci disponibili diversi tipi di buffer collegato al pin: ad esempio, il

pin relativo al INT0 è uno Schmitt Trigger (allo scopo di squadrare

al meglio il segnale) quando opera in questa funzione è un gate a livello

logico TTL quando agisce come pin di ingresso GPIO.

|

Pin

|

Funzione

|

TRIS

|

I/O

|

Tipo

|

Descrizione

|

|

RB0

INT0

FLT0

AN12

|

RB0

|

0

|

O

|

DIG

|

LATB<0> uscita digitale

|

|

1

|

I

|

TTL

|

PORTB<0> ingresso digitale

|

|

INT0

|

1

|

I

|

ST

|

ingresso interrupt esterno 0

|

|

FLT0

|

1

|

I

|

ST

|

ingresso enhanced PWM (modulo

ECCP1)

|

|

AN12

|

1

|

I

|

ANA

|

ingresso

analogico canale 12

|

|

RB1

INT1

AN10

|

RB1

|

0

|

O

|

DIG

|

LATB<1>

uscita digitale

|

|

1

|

I

|

TTL

|

PORTB<1>

ingresso digitale

|

|

INT1

|

1

|

I

|

ST

|

ingresso

interrupt esterno 1

|

|

AN10

|

|

|

ANA

|

ingresso

analogico canale 10

|

|

RB2

INT2

AN8

|

RB2

|

0

|

O

|

DIG

|

LATB<2>

uscita digitale

|

|

1

|

I

|

TTL

|

PORTB<2>

ingresso digitale

|

|

INT2

|

1

|

I

|

ST

|

ingresso

interrupt esterno 2

|

|

AN2

|

1

|

I

|

ANA

|

ingresso

analogico canale 8

|

|

RB3

AN9

CCP2

|

RB3

|

0

|

O

|

DIG

|

LATB<3>

uscita digitale

|

|

1

|

I

|

TTL

|

PORTB<3>

ingresso digitale

|

|

AN9

|

1

|

I

|

ANA

|

ingresso

analogico canale 9

|

|

CCP2

|

0

|

O

|

DIG

|

uscita

CCP2 compare e PWM

|

|

1

|

I

|

ST

|

ingresso

cattura CCP2

|

|

RB4

KBI0

AN11

|

RB4

|

0

|

O

|

DIG

|

LATB<4>

uscita digitale

|

|

1

|

i

|

TTL

|

PORTB<4>

ingresso digitale

|

|

KBI0

|

1

|

I

|

ST

|

ingresso interrupt on change 0

|

|

AN11

|

1

|

I

|

ANA

|

ingresso

analogico canale 11

|

|

RB5

KBI1

PGM

|

RB5

|

0

|

O

|

DIG

|

LATBB<5>

uscita digitale

|

|

1

|

I

|

TTL

|

PORTB<5>

ingresso

digitale

|

|

KBI1

|

1

|

I

|

ANA

|

ingresso interrupt on change 1

|

|

PGM

|

1

|

I

|

ST

|

ingresso programmazione low voltage

LVP

|

|

RB6

KBI2

PGC

|

RB6

|

0

|

O

|

DIG

|

LATB<6>

uscita digitale

|

|

1

|

I

|

TTL

|

PORTB<6>

uscita digitale

|

|

KBI2

|

1

|

I

|

TTL

|

ingresso interrupt on change 2

|

|

CLKO

|

-

|

I

|

ST

|

clock input per ICSP e ICD

|

|

RB7

KBI3

PGD

|

RB7

|

0

|

O

|

DIG

|

LATB<7>

uscita digitale

|

|

1

|

I

|

TTL

|

PORTB<7>

uscita digitale

|

|

KBI3

|

1

|

I

|

DIG

|

ingresso interrupt on change 2

|

|

PGD

|

-

|

I

|

ST

|

dati seriali per ICSP e ICD

|

- = non dipende dal registro TRIS

DIG = uscita digitale

TTL = buffer di ingresso livello logico

ST = ingresso con trigger di schmitt

ANA = ingresso (uscita) analogico

I pin di PORTB

posso assumere le seguenti funzioni :

-

GPIO (RB7:0)

Si tratta della funzione generica di ingresso/uscita (GPIO General

Purpose IO), dove la direzione è stabilita dal solito registro TRIS. PORTB

è il registro dello stato della porta (in lettura e scrittura), mentre

LATB è il registro del latch della porta in uscita.

-

ADC (AN12:8)

La funzione ADC (Analog to Digital Converter) coinvolge i pin RB4:0.

La sua operatività dipende dal registro ADCON1.

(ved. Modulo AD).

Inoltre è possibile stabilire a priori nella configurazione (bit PBADEN

del registro CONFIG3H)

lo stato di default che avranno questi pin dopo il POR :

PBADEN = ANA

abilita la funzione analogica come default al POR

I bit 0:3 di ADCON1 a

livello 0 confermano la funzione analogica (default al POR).

Se posti a 1, riportano i pin ad una funzione GPIO

PBADEN = DIG

disabilta la funzione analogica al POR.

E' possibile stabilire la funzione dei pin agendo sui

corrispondenti bit di ADCON1. Ad esempio, per abilitare PB4:0 come

GPIO digitali , le istruzioni tipiche sono :

movlw

0x07

movwf

ADCON1

-

external interrupt (INT2:0)

Alcuni pin di PORTB

(RB2:0) possono assumere la funzione di generatori di

chiamata ad interrupt sul fronte di salita o discesa di un segnale

esterno . (ved. Interrupt non periferici).

-

interrupt on change (KBIO3:0)

Alcuni pin di PORTB

(RB7:4) possono assumere la funzione di generatori di chiamata ad

interrupt sulla variazione di stato . (ved. Interrupt non periferici).

-

enhanced PWM fault del modulo ECCP1

Il pin RB0 può essere dedicato come ingresso di Fault del modulo

ECCP1

-

CCP e out PWM del modulo CCP2

Il pin RB3 può essere

dedicato come uscita del modulo CCP2. La funzione di RB3 come

uscita /ingresso per il modulo CCP2 è alternativa a quella di RC1, che

è il default del POR ed è stabilita in fase di configurazione dal bit CCP2MX

del registro CONFIG3H

.

PGD/PGC/PGM di ICD/ICSP

Come comune per i PIC, RB7:6 sono dedicabili alla programmazione in

circuit (ICSP) e al debug (ICD). Le funzioni sono stabilite esclusivamente

in fase di configurazione dai bit

!DEBUG e LVP

del registro CONFIG4L.

In modo debug il funzionamento di RB7:6 non dipende dal registro TRISB

ed esclude qualsiasi altra assegnazione. Ad esempio, impostando il PORTB

Change interrupt, in modo debug solamente PB5:4 saranno operativi.

Pull-up

: Sul PORTB è inclusa la possibilità di attivare un pull up interno

denimonato weak pull-up..

Anche per PORTB

il default del POR fa assumere ai registri particolari valori pre definiti

e questo rende indispensabile, nelle prime fasi di inizializzazione dell'

hardware, dedicare una parte alla corretta definizione delle funzioni di

questi pin.

ATTENZIONE:

Anche per PORTB

il default del POR fa assumere ai registri particolari valori pre

definiti e questo rende indispensabile, nelle prime fasi di

inizializzazione dell' hardware, dedicare una parte alla corretta

definizione delle funzioni di questi pin.

|

I registri associati a PORTB

A causa delle numerose funzioni implementabili, svariati

registri sono associati associati all' uso di PORTB

sono i seguenti :

|

Nome

|

bit 7

|

bit 6

|

bit 5

|

bit 4

|

bit 3

|

bit 2

|

bit 1

|

bit 0

|

|

PORTB

|

RB7

|

RB6

|

RB5

|

RB4

|

RB3

|

RB2

|

RB1

|

RB0

|

|

LATB

|

Data latch

|

|

TRISB

|

Data direction

- 1 = input / 0 = output

|

|

INTCON

|

|

|

|

INT0IE

|

RBIE

|

|

INT0IF

|

RBIF

|

|

INTCON2

|

!RBPU

|

INTEDG0

|

INTEDG1

|

|

|

|

|

RBIP

|

|

INTCON3

|

INT2IP

|

INT1IP

|

|

INT2IE

|

INT1IE

|

|

INT2IF

|

INT1IF

|

|

ADCON1

|

|

|

|

|

PCFG3

|

PCFG2

|

PCFG1

|

PCFG0

|

|

CONFIG3L

|

|

|

|

|

|

|

PBADEN

|

|

|

CONFIG4L

|

!DEBUG

|

|

|

|

|

LVP

|

|

|

I bit non indicati non sono usati dalla gestione di PORTB.

Situazione al POR

Al POR:

-

TRISB

= 11111111, ovvero la direzione generale dei pin è come ingresso.

-

PORTB

e LATB

hanno contenuto indeterminato.

-

In ADCON1

il valore dei bit PCFG<3:0>

è determinato dal valore di PBADEN

:

- se PBADEN = 1 , PCFG3:0

= 0000, ovvero AN12:0 programmati come input analogici

- se PBADEN = 0 , PCFG3:0

= 0111, ovvero AN7:0 programmati come input analogici

Per quanto riguarda i registri di controllo dell' interrupt,

al POR:

-

!RBPU = 1 , ovvero

pull-up disabilitati

-

INTEDG1:0 = 1 ,

ovvero direzione del fronte di salita (rising edge)

-

RBIP/INT2IP/INT1IP

= 1 , ovvero priorità alta

Tutti gli Interrupt sono disabilitati

Nei registri di configurazione, per default :

-

PBADEN = 1 , ovvero PORTB<4:0>

come ingressi analogici al POR

-

!DEBUG e LVP

= 1 , ovvero entrambi disabilitati

Per quanto riguarda le funzioni speciali (ADC, Interrupt INT

e PORTB Change, CCP, ICSP , ICD e LVP) consultare i capitoli relativi.

Si può riassumere la situazione del POR in questo modo :

-

I pin sono configurati come ingressi digitali e, in

parte, analogici, se PBADEN

non viene nominato nella configurazione. La funzione può essere

modificata con ADCON1.

-

Se nella configurazione PBADEN

viene programmato a 0, tutti i pin di PORTB

saranno GPIO digitali. La funzione può essere modificata con ADCON1.

Ne consegue che , in ogni caso, è opportuno inserire nel sorgente

una riga di configurazione per PBADEN

in modo da avere ben chiara la situazione dei PORTB<4:0>.

-

I pull-up sono disabilitati e, se richiesti, occorre

abilitarli da programma

-

Nessun interrupt è abilitato. I bit di livello della

priorità assegnano per default la priorità elevata. L'

abilitazione e una diversa attribuzione di livello deve essere fatta da

programma.

-

Le funzioni DEBUG

e LVP sono

disabilitate e, se richieste, vanno abilitate con opportune linee di

configurazione nel sorgente.

-

Nessuna funzione speciale è abilitata per default sul PORTB

Inizializzazione di PORT

B

Una sequenza di inizializzazione come GPIO digitale può

essere questa

:

;

Inizializza

PORT B

clrf LATB

; clear PORTB latch

movlw 0x07

; tutti i pin come digital GPIO

movwf ADCON1

; (richiesto se PBADEN è abilitato)

movlw b'11001111'

; set RB7:6 e RB3:0 come input

movwf TRISB

; e RB5:4 come out |

Anche qui alcuni punti sono importanti in quanto l' errata

inizializzazione sia del TRIS che dei registri di configurazione e del

registro ADCON1

impedisce l' uso dei pin nel modo voluto.

Il default al POR configura i PORTB<4:0> come ingressi analogici e i

PORTB<7:5> come ingressi digitali.

Per evitare l' assegnazione analogica occorre configurare PBADEN

= 0 oppure agire sull' ADCON1

come nell' esempio precedente.

I pull-up

PORTB

dispone di un set di pull up che possono essere attivati sotto controllo del

programma.

La loro presenza rende inutili pull up esterni in molte situazioni.

Principalmente sono pensati come supporto alla funzione PORTB Change per un

uscita dal modo sleep a causa di un segnale esterno (tastiera) e prendono il

nome di weak pull-up.

Il bit di controllo è !RBPU

(INTCON2<7>)

. Va osservato che la posizione di questo bit è diversa nei mid range, dove

fa parte dell' OPITION register , che non esiste più nei PIC18 ; quindi si

richiede una modifica nella conversione di un sorgente da mid-range a

enhanced.

In ogni modo la logica di funzionamento è analoga per cui :

Nella famiglia PIC18F43xx i pull up sono abilitati e

disabitati su tutti i pin contemporaneamente. Altri PIC consentono il

controllo di ogni singolo pin.

Dal data sheet non risulta un valore specifico per i weak

pull-up, in quanto non si tratta di resistenze fisiche, ma di sorgenti di

corrente FET a canale P ad alta resistenza, il cui valore varia con la

temperatura e le caratteristiche costruttive. Il foglio dati indica un

range di corrente tra 50 e 400uA (tipico 200 uA) a 5V, equivalenti ad una

resistenza tra 12k e 100k (typ. 25k).

Nel caso in cui vengano usati pull-up esterni, quelli integrati vanno

disabilitati.

I pull-up integrati sono disabilitati automaticamente per i

pin configurati come output.

Al POR i pull-up sono per default disabilitati.

NOTE:

-

Per default al POR i registri che interessano

PORTB assumono valori ben definiti, che possono non essere

quelli richiesti dal programma

-

TRISB configura al POR tutti i pin come

ingressi

-

Per default la configurazione attiva PBADEN

e quindi le funzioni di ingresso analogico. Se non sono

richieste occorre agire nel' inizializzazione della porta con ADCON1

oppure nel CONFIG disabilitando PBADEN (PBADEN=DIG).

-

Al POR i pull-up sono disabilitati. Se

necessario occorre abilitarli da programma

-

Occorre verificare con cura il valore da

attribuire a TRIS per avere disponibile la funzione voluta:

ad esempio i pin usati come ingressi dell' interrupt esterno

vano configurati come input.

Dimenticando questi particolari si potranno avere

problemi nel funzionamento dei pin

|