PSP - Parallel Slave Port

Questa funzione, per molti, risulta enigmatica e, in effetti, non è molto

conosciuta, nè comune.

In pratica, la Parallel Slave Port è un mezzo di comunicazione

tra un

microprocessore

e il PIC, che opera come slave.

Ed in effetti va

ricordato che il progenitore dei PIC attuali (il PIC1640 di General Instruments) era proprio

previsto per essere utilizzato come una periferica intelligente sul bus di

altri microprocessori.

Possiamo

caratterizzare i due ambienti così:

| microprocessore - uP |

i componenti del sistema (memoria

e periferiche) sono esterni alla CPU, a cui sono collegati

con i bus |

| microcontroller - uC |

i

componenti del sistema (memoria, periferiche, bus) sono tutti

contenuti all' interno di un singolo chip (embedded) |

Trovate qui

una trattazione più dettagliata dell' argomento.

I due sistemi sono dedicati ad applicazioni

di complessità differente:

-

un sistema a microcontroller è

essenzialmente preposto all' automatizzazione/automazione di un qualche dispositivo o

processo limitato (regolatori di velocità, orologi, temporizzatori,

controller di periferiche, rilevamento di segnali, elettrodomestici, auto, ecc.). Si tratta di

applicazioni dedicate, cost sensitive, non espandibili.

-

un sistema a microprocessore prevede una possibilità di espansione, una

disponibilità ampia di periferiche e memoria, una capacità di elaborazione

elevata e si presta per ambiti di controllo e automazione più complessi

(personal computer, PLC, controlli di processo, telcomunicazioni, ecc.)

Nella gamma delle periferiche associabili ad un sistema a

microprocessore trovano posto periferiche "intelligenti",

ovvero in grado di svolgere funzioni complesse sotto il controllo del

microprocessore, ma in modo autonomo rispetto alle sue risorse.

Questo è, appunto, la collocazione del modulo PSP, ovvero

quella di permettere la comunicazione tra microcontroller (periferica

intelligente) e microprocessore, attraverso il bus dati di quest' ultimo.

|

Schematizzando la struttura del sistema a microprocessore,

troviamo:

- un bus DATI

- un bus INDIRIZZI

- e un bus di CONTROLLO

Ogni periferica esterna alla CPU è indirizzata dal bus

INDIRIZZI, attraverso delle logiche di CS (chip select) e scambia i

dati sul bus DATI, sotto il controllo dei segnali RD (Read) e WR (Write)

generati dal microprocessore e inviati sul bus di CONTROLLO. |

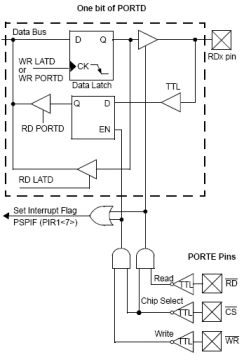

Il PIC che dispone

del modulo PSP utilizza il suo PORTD per connettersi in modo

parallelo al bus dati, dove le

informazioni sono scambiate in parallelo, sotto il controllo dei segnali

!RD, !WR e !CS, che sono

forniti dal master:

Va compreso che

questa funzione di slave riguarda la comunicazione dei dati dal PIC verso il

microprocessore e viceversa, comunicazione che avviene su richiesta del

microprocessore e con le temporizzazioni date dai segnali del bus. Per il

resto il PIC lavora nel suo solito modo, collezionando i dati da inviare al

bus o eseguendo i comandi ricevuti attraverso il bus.

Dunque, dovrebbe

essere ora chiaro cosa sia PSP: è una porta parallela a 8 bit per

scambiare dati con un ambiente "master" esterno.

|

La struttura hardware del

PORTD è leggermente diversa dalle altre in quanto, nel momento in cui

è abilitata la funzione PSP, sono dei segnali esterni WR, RD e CS

quelli che vanno a gestire lo scambio dei dati:

- WR: a livello 0

abilta il data latch in ingresso del microcontroller e carica il

dato fornito sul bus del microprocessore

- RD: a livello 0 abilita il

gate tree state di uscita dei dati dal latch dati verso il bus

esterno del microprocessore

- CS: a livello 0

abilita le funzione RD o WR

Contemporaneamente, i

segnali RD o WR generano una richiesta di interrupt settando il flag

PSPIF.

La logica di ingresso dei

segnali WR,RD e CS sono inverter a livello TTL.

Da ricordare che, data la necessità di un PORTD

a 8 bit completi,

la funzione PSP non è disponibile per PIC in packages minori di 40 pin.

|

Il latch dei dati di lettura e quello di scrittura del PSP si

trovano allo stesso indirizzo, come registro PORTD.

Però, in pratica, si

tratta di due diversi buffer, per cui:

-

scrivendo PORTD non si sovra scrive un

eventuale dato inviato dal master e

-

leggendo PORTD non si legge il dato in uscita, ma l' ultimo inviato dal master.

La scrittura di PORTD non si traduce nell' apparire dei corrispondenti

livelli di tensione sui pin se non nel momento in cui il master richiederà

la lettura.

Questo vale solamente quando PORTD funziona come PSP,

mentre in GPIO si tratta di una struttura uguale a quella degli altri port.

Le

temporizzazioni tra i segnali sono tali da potersi adattare con poca

circuiteria esterna ai bus dei principali microprocessori.

In

scrittura, il microprocessore seleziona la periferica mandando bassa la

linea CS relativa e quindi invia i dati sul bus dati, sincronizzato dal

segnale WR. Il PIC riceve l' informazione dell' arrivo dei dati, che sono

conservati nel latch dati fino alla prossima scrittura, attraverso il flag

PSPIF e IBF

, che

vanno a 1 al termine della fase Q3 successiva alla chiusura del segnale WR

(figura 10.3).

In pratica, i dati forniti dal master sono scritti sul PORTD quando

sia

!CS che !WR sono a livello basso; i bit PSPIF di interrupt e il flag IBF

(TRISE7) sono settati al termine della scrittura, permettendo al programma

la cattura dei dati. IBF a livello 1 indica che un dato è stato scritto dal

master sul PSP ed attende di essere letto

ed

è azzerato dalla lettura del

dato presente sul PSP da

parte del PIC.

Il lettura,

analogamente, il microprocessore seleziona la periferica con CS e richiede

l' emissione dei dati con il segnale RD. Il PIC

ha preparato il dato

nel buffer e all' arrivo di

RD i dati sono passati al bus esterno;

la conclusione dell' operazione è segnalata dal

flag PSPIF.

I dati diretti al

master sono letti con !RD e !CS a livello basso; in tal caso oltre a

PSPIF, il flag relativo è OBF (TRISE6)

che va a 0 non appena è

ricevuto il segnale RD dal

master (figura 10-4).

Al termine della fase Q3

successiva alla chiusura del segnale RD, il flag PSPIF sarà settato.

In pratica, prima di scrivere un nuovo dato

nel latch del PSP,

il programma deve verificare che il precedente

sia stato letto, onde evitare un overflow;

nel caso in cui sia stato ri scritto PORTD mentre il

dato precedentemente non era ancora stato letto

(il dato

precedente viene sovra

scritto e va perduto) è

segnalato dal flag IBOV

(TRISE5) che va a 1.

IBOV deve essere azzerato da software prima della prima scrittura,

caso mai si

trovasse a 1. Prima di una successiva scrittura, va letto per assicurarsi

che sia a zero, ovvero che il dato precedente è stato trasmesso

regolarmente. Viene rimesso a zero solo via software.

I valori dei tempi sono riportati nella Table 26-13 delle

caratteristiche AC (pag.353).

Per utilizzare questa modalità occorre :

come GPIO e non come ingressi

analogici :

movlw b'11111111'

; port A & E come digitali

xorwf ADCON1 |

programmare PORTE2:0 come ingressi

(WR, RD e CS sono generati dal master) attraverso i bit 2:0

di TRISE:

movlw b'00000111'

; port E come input

xorwf TRISE |

abilitare il bit PSPMODE (TRISE<4>)

:

Utilizzando la funzione PSP, il registro TRISD non ha

nessuna funzione, in quanto la direzione del PORTD viene stabilita dai

segnali di controllo che arrivano dal master.

Riassumendo:

movlw

b'00000111'

; port E come digitali

xorwf ADCON1

movlw b'00000111'

; port E come

input

xorwf TRISE

bsf PSPCON, PSPMODE ; abilita PSP

bsf TRISE, PSPMODE |

Le operazioni di PSP sono gestite in interrupt

in quanto si suppone di avere a che fare con una comunicazione molto rapida;

inoltre si tratta di un sistema di scambio dati asincrono gestito dal master

esterno

a cui

il PIC si deve

sincronizzare. Quindi

questa

la via più adeguata, anche se teoricamente è possibile un polling

dei flag..

L' interrupt è chiamato quando la scrittura o la lettura da parte del

master sono completate.

-

Il bit di abilitazione dell' interrupt è PSPIE

(PIE1<7>) che va posto a 1 se si desidera attivare l' interrupt

della porta PSP.

-

Il bit di selezione della priorità dell' interrupt è

PSPIP (IPR1<7>).IPIR1 è a 1 se si desidera l' alta priorità,

altrimenti va a posto a 0. L' abilitazione del modo interrupt con

priorità richiede di aver settato il bit IPEN (RCON<7>) ;

altrimenti viene impiegato un sistema di interrupt senza livelli di

priorità e l' impostazione di PSPIP è indifferente.

-

Il flag di identificazione è PSPIF (PIR1<7>) che

va a 1 a seguito delle operazioni di scrittura o lettura del master.

PSPIP va cancellato da software.

Il programma di gestione della PSP deve, una volta settato

abilitato relativo, attende la richiesta e distingue le operazioni di

lettura da quelle di scrittura analizzando i flags.

Un esempio della struttura di una comunicazione PSP tra un

processore esterno e il PIC può essere schematizzata così :

-

Il processore master seleziona l' indirizzo del suo bus

a cui corrisponde il PIC. Questo provoca un livello basso sul pin !CS

-

il processore master scrive un dato che sarà catturato

nel latch del PSP in seguito al segnale !WR

viene generata

una richiesta di interrupt nel PIC

il programma di

gestione verifica il flag PSPIF e se settato, riconosce una chiamata

interrupt da PSP

la verifica dei

flag IBF e OBF permette di selezionare se si tratta di lettura o

scrittura. Se IBF è a 1, il programma legge PORTD con un movf

PORTD, W ; questo provoca il clear del flag IBF

il valore letto su PORTD non è lo stato fisico dei pin,

ma il dato che il master ha scritto e che è stato catturato nel buffer.

l' uscita dall' interrupt richiede la cancellazione del

flag PSPIF

Nel caso in cui il master scriva un secondo dato prima che

il PIC abbia letto il primo, il flag IBOV verrà settato, indicando un

overflow. Il primo dato è sovra scritto dal secondo e va perduto.

Nel caso di una lettura da parte del master:

-

il PIC prepara il dato da inviare scrivendolo nel PORTD.

Questo provoca un livello 1 sul flag OBF. In sostanza OBF indica che c'è

un dato pronto per essere inviato. OBF va testato prima di scrivere

PORTD per evitare di sovrascrivere un dato non ancora inviato

-

Quando il master seleziona il PIC e richiede una lettura

con !RD, il PORTD passa in uscita e il dato viene letto sul bus del

master. Il flag OBF viene cancellato.

-

Contemporaneamente viene inviata la richiesta di

interrupt che avvisa il PIC che è disponibile il buffer per caricare un

nuovo dato.

-

Ancora una volta PSPIF va cancellato da programma