Inoltre, per il controllo dell'

interrupt, sono disponibili i soliti tre bit IE/IF/IP, secondo la

tabella seguente :

| Registro |

Bit

7 |

Bit

6 |

Bit

5 |

Bit

4 |

Bit

3 |

Bit

2 |

Bit

1 |

Bit

0 |

| PIR1 |

- |

- |

- |

- |

- |

|

TMR1IF |

- |

| PIE1 |

- |

- |

- |

- |

- |

|

TMR1IE |

- |

| IPR1 |

- |

- |

- |

- |

- |

|

TMR1IP |

- |

La presenza dei bit di controllo nei registri PIR/PIE/IPIR

indica che si tratta di un interrupt periferico, che necessita per la sua

abilitazione dei entrambi gli switch globali GIE/PEIE.

Registri di conteggio di TIMER1

I diagrammi seguenti schematizzano il funzionamento di Timer0 nel

funzionamento di default con due istruzioni a 8 bit per caricare i

registri di conteggio T

MR1H:L

:

e in quello con una unica operazione a 16 bit :

Il conteggio viene immagazzinato in una coppia di registri, TMR1H:L.

Sono programmabili due modi per leggere e scrivere questi registri:

- Il primo modo, default al POR, prevede che TMR1H

e TMR1L

sia due registri separati il cui caricamento o lettura richiede singole

operazioni a 8 bit. Questo rende Timer1 analogo a quello della famiglia

PIC16F.

- Nel secondo modo, ovvero portando il bit RD16

(T1CON<7>)

a 1, l' indirizzo del registro TMR1

H

è mappato in buffer. Una lettura di TMR1L

carica il contenuto del counter alto nel buffer in modo da evitare problemi

di lettura con il timer in funzione. Analogamente, la scrittura di TMR1H

avviene nel buffer, che sarà trasferito al registro di conteggio al momento

della scrittura di TMR1L.

Questo consente di caricare il contatore a 16 bit con una unica operazione,

evitando gli errori che si avrebbero con una operazione in più fasi e il

timer in funzione.

Da notare che il contenuto di conteggio del prescaler viene azzerato alla

scrittura di TMR1L,

iniziando un ciclo di lavoro interamente nuovo.

La modalità a 16 bit va impiegata in quelle situazioni in cui è critica la

precisione nel ri aggiornamento del contenuto dei registri di conteggio.

In ogni caso il contatore viene incrementato ad ogni transizione del clock che

può essere filtrata dal prescaler.

Timer1 include un proprio oscillatore da completare con componenti esterni

(condensatori, cristallo, resistenza) che può servire sia da sorgente del

clock per il timer stesso sia da clock alternativo per l' intero sistema. In

questo caso, la sua funzione è fornire un clock a basso consumo per

operazioni RTC.

Una Silicon Errata comunica che, quando TImer1 viene avviato o aggiornato,

richiede che ci sia una transizione alto basso del clock prima iniziare il

conteggio sul fronte di salita successivo; se l' aggiornamento dei registri

del timer non è completato prima del fronte di discesa, andrà perso un

impulso.

Per evitare questo problema occorre aggiornare i registri del timer prima del

fronte di discesa del clock oppure attendere che TMR1L

sia incrementato e quindi aggiornare immediatamente i registri.

Per questo motivo non è consigliato usare Timer1 in interrupt a bassa priorità

quando la correttezza del conteggio è critica, in quanto un eventuale

interrupt ad alta priorità potrebbe intervenire ad alterare il corretto

processo di scrittura dei registri.

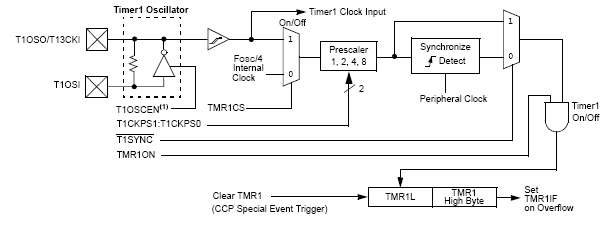

Timer1 può operare come timer come counter sincronizzato o asincrono. Il

modo è determinato da TMR1

CS

(T1CON<1>).

Quando questo bit è 0 il timer incrementa ad ogni ciclo del clock interno (Fosc/4).

Quando il bit è a 1 il timer incrementa ad ogni fronte di salita (rising edge)

dell' ingresso esterno del clock o del suo oscillatore.

L' oscillatore esterno di TIMER1

Se viene abilitato il circuito di clock, i pin GPIO RC0

e RC1 diventano

rispettivamente T1OSI e T1OSO,

indipendentemente dal valore assegnato a TRISC1:0

.

L' oscillatore di Timer1 è abilitato con T1OSCEN

(T1CON<3>). Il

circuito è il seguente :

|

Microchip intende questo

oscillatore come utilizzabile con quarzi per RTC, tipicamente 32768 Hz.

Non ci sono però indicazioni sulla massima frequenza utilizzabile, che,

probabilmente, può raggiungere valori maggiori. |

Questo, però è poco

significativo, in quanto l' oscillatore di Timer 1 ha funzioni alternative a

quello primario proprio per il contenimento del consumo, che si ottiene

generando una frequenza minore di quella dell' oscillatore primario.

Nulla viene specificato nei fogli dati riguardo all' uso del pin T1OSI

che , stando agli schemi, può essere usato anche come ingresso per una

sorgente di clock completamente esterna al processore. In questo caso, da T1OSO

si ottiene la stessa frequenza in uscita.

Viene invece evidenziato come il valore dei condensatori applicati al

cristallo o risonatore sia significativo sulla stabilità (maggior capacità,

maggiore stabilità) , ma anche sul tempo di assestamento dell' oscillatore,

ovvero del tempo necessario ad ottenere il clock corretto dal momento della

messa in servizio dell' oscillatore (maggiore la capacità, maggiore il tempo

di assestamento)

Nelle modalità a gestione del consumo, i bit SCS1:0

(OSCON<1:0>)

configurati al valore 01 permettono il passaggio sull' oscillatore di Timer 1

come fonte del clock del suistema : CPU e periferiche saranno alimentate da

questo clock.

Se il bit IDLEN (OSCON<7>)

è a zero e viene eseguita una istruzione SLEEP, il sistema entra in modalità

SEC_IDLE .

Fino a che il clock di Timer1 è operativo, il flag T1RUN

(T1CON<6>)

è a livello 1 e questo può essere usato per verificare quale sia la sorgente

del clock al momento. Indica anche che la sorgenet del clcok è usata dal Fail

Safe Clock Monitor.. Se il CLock Monitor è abilitato e l' oscillatore di

Timer 1 ha problemi, la verifica di T1RUN

indica se il clock è fornito dal timer o da un' altra sorgente.

L' oscillatore di Timer 1 può essere programmato per due livelli di

consumo. Se il bit LPT1OSC

è a 1, l' oscillatore funziona alla minima potenza, mentre se è a 0 (default)

opera a potenza normale. In modalità low power c'è una maggiore sensibilità

ai disturbi, che possono alterare il funzionamento dell' oscillatore. Per un

consumo minore, le impedenze in gioco dovranno essere maggiori e questo riduce

l' immunità ai disturbi : in particolare dovrà essere curata la struttura

del circuito stampato, ad esempio prevedendo anelli di massa per schermare i

pin dell' oscillatore da eventuali circuiti ad alta frequenza vicini (ad

esempio l' ingresso degli impulsi CCP1 o PWM).

In base a quanto notato, allora, la corretta sequenza di lettura sarà

quella di leggere prima TMR1L

e poi TMR1H,

mentre per la scrittura, si scriverà prima TMR1H e poi TMR1L.

E' sottinteso che se se viene scritto solo TMR1H

senza riscrivere anche TMR1L,

il trasferimento del valore impostato per TMR1H

non avrà effetto. Così pure leggendo prima TMR1H

non si avrà il giusto valore conteggiato in quel momento.

Il Prescaler

Il prescaler di Timer1 è interamente dedicato a questo timer e non è

condiviso con altre funzioni. Non necessita di bit di abilitazione in quanto,

a differenza di quello di Timer0, dispone della scelta di un

"divisore" 1:1. I bit TCKPSA1:0

(T1CON<5:4>)

permettono la selezione di 4 valori del rapporto

Il prescaler, sia come assegnazione che come divisore, è interamente sotto

controllo del software e può essere variato a piacere durante l' esecuzione

del programma.

Interrupt

Timer1 può essere una fonte di richiesta di interrupt, che è generato

quando il registro di conteggio passa da 0xFF a 0x00 in modo a 8 bit o da

0xFFF a 0x0000 in modo 16 bit.

Questo overflow setta il bit TMR1IF

(PIR1<1>). La

richiesta di interrupt può essere mascherata con il bit TMR1IE

(PIE1<1>). Prima di

riabilitare l' interrupt, TMR1IF

deve essere portato a zero da programma.

Timer1 è in funzione anche in modalità Sleep e può essere una sorgente

di wake-up

La gestione interrupt del Timer1 richiede :

- l' abilitazione del bit TMR1IE

(PIE1<1>),

che va posto a 1 se si

desidera attivare l' interrupt

- Il bit di selezione della

priorità dell' interrupt è TMR1IP

(IPIR1<1>).

E' a 1 se si desidera l' alta priorità, altrimenti va a posto a 0. L'

abilitazione del modo interrupt con priorità richiede di aver settato il

bit IPEN (RCON<7>)

; altrimenti viene impiegato un sistema di interrupt senza livelli di

priorità e l' impostazione di TMR1IP

è indifferente.

- Il flag di identificazione è TMR1IF

(PIR1<1>)

che va a 1 a seguito all' overflow del counter e va cancellato da

software.

L' interrupt di Timer1 fa riferimento al registro PIR1

e quindi è considerata una interruzione periferica e quindi sono

dipendenti per l' abilitazione da PEIE.

Una applicazione RTC

Il foglio dati propone una applicazione RTC del Timer1 , usato con un

cristalli da 32768 Hz. Questo permette di disporre di un orologio senza la

necessità di aggiungere periferiche esterne, dato che il basso consumo ed il

funzionamento anche nel modo SLEEP permettono l' impiego con batterie u super

condensatori.

La routine RTCisr dimostra un metodo

semplice per incrementare un contatore ad intervalli di 1 secondo in interrupt.

Contatori per minuti, ore e calendario potranno essere aggiunti con facilità.

Poichè si sta lavorando in modalità 16 bit, i registri di conteggio vanno

in overflow dopo circa 2 secondi. Per forzare l' overflow ad 1 secondo occorre

pre caricare i registri con un valore adeguato. L' aggiustamnento di questo

valore correggerà differenze possibili nel valore della frequenza di

oscillazione del cristallo.

L' esempio tiene conto del documento Timer1 errata , documento Microchip

DS80329A.

RTCinit

MOVLW 80h

; Preload TMR1 register pair

MOVWF TMR1H

; for 1 second overflow

CLRF TMR1L

MOVLW b’00001111’

; Configure for external clock,

MOVWF T1CON

; Asynchronous operation, external oscillator

CLRF secs

; Initialize timekeeping registers

CLRF mins

MOVLW .12

MOVWF hours

BSF PIE1,

TMR1IE ; Enable Timer1

interrupt

RETURN

RTCisr:

btfsc TMR1L,

0 ; wait for TMR1L<0> to

become clear

bra $-2

btfss TMR1L,

0 ; wait for TMR1L<0> to

become set

bra $-2

; If TMR1 update can be completed before clock pulse

; goes low, start update here

Update:

bsf TMR1H,7

; Preload for 1 sec overflow

BCF PIR1,

TMR1IF ; Clear interrupt

flag

INCF secs, F

; Increment seconds

MOVLW .59

; 60 seconds elapsed?

CPFSGT secs

RETURN

; No, done

CLRF secs

; Clear seconds

INCF mins, F

; Increment minutes

MOVLW .59

; 60 minutes elapsed?

CPFSGT mins

RETURN

; No, done

CLRF mins

; clear minutes

INCF hours, F

; Increment hours

MOVLW .23

; 24 hours elapsed?

CPFSGT hours

RETURN

; No, done

CLRF hours

; Reset hours

RETURN

; Done