Il modo PWM

In modo PWM (Pulse Width Modulation) il modulo CCP lavora con una

risoluzione a 10 bit.

l diagramma a blocchi seguente riassume il funzionamento del modo PWM :

|

La funzione è legata al Timer2.

Essendo il timer 2 a 8 bit, il suo valore è concatenato con con altri

due bit dipendenti dal clock Q interno o dal prescaler per arrivare ai

10 bit.

L' uscita del segnale PWM è disponibile sul pin

CCP

che è stato

scelto (RB3 o RC1).

|

Anche in questo caso, per usare il pin CCP in uscita, occorre programmare

opportunamente il relativo bit del TRIS della porta. In caso contrario, non

ci sarà uscita disponibile.

Cancellando il contenuto del registro CCP2CON, il pin CCP corrispondente

(RB3 o RC1) sarà portato a livello basso. Questo non dipende dai latch dei

PORT B o C .

Nel segnale

PWM sono definiti due elementi

principali :

|

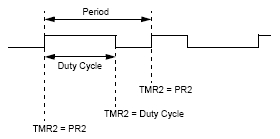

- il Periodo è la distanza in tempo tra due fronti di salita.

- Il Duty Cycle è il tempo di un periodo attivo.

- La frequenza del PWM è uguale a 1 / Periodo

|

Il Periodo del PWM è calcolabile come :

Periodo PWM = [(PR2)+1] * 4 * Tosc * (Prescaler TMR2)

Nella funzione di PWM il post scaler di Timer2 non viene utilizzato.

Quando TMR2 è uguale a PR2 si verificano i seguenti tre eventi :

- TMR2 è azzerato

- il pin CCPx è portato a 1 (fa eccezione il caso in cui il Duty Cycle

sia posto a 0)

- il Duty Cycle del PWM è copiato da CCPRxL a

CCPRxH

Il Duty Cycle del PWM viene specificato scrivendo il registro CCPRxL (8 bit

più significativi) ed i bit CCPxCON<5:4> (2 bit meno significativi),

per un totale di 10 bit di risoluzione.

Il valore del Duty Cycle è dato dalla seguente espressione :

Duty Cycle PWM = (CCPRxL:CCPxCON<5:4>) * Tosc *

(Prescaler TMR2)

CCPRxL e

CCPRxCON<5:4> possono essere scritti in qualsiasi

momento, ma il valore imposto al Duty Cycle non viene trasferito in CCPRxH se

non dopo una uguaglianza tra PR2 e TMR2.

Nel modo PWM, il registro CCPRxH è a sola lettura; questa struttura a buffer

ha lo scopo di evitare impulsi spuri (glitches) nel segnale PWM.

Quando CCPRxH e il latch dei due bit minori eguaglia

TMR2, concatenato con

un Q clock interno a 2 bit o con il prescaler di TMR2, il pin

CCPx è portato

a 0.

La massima risoluzione in bit del PWM è data dalla seguente espressione :

Risoluzione massima PWM = log(Fosc/Fpwm) / log(2)

La tabella seguente da una idea delle possibilità :

| Frequenza del PWM |

2.44kHz |

9.77kHz |

39.6kHz |

158.25kHz |

312.5kHz |

416.67kHz |

| Prescaler del Timer2 |

16 |

4 |

1 |

1 |

1 |

1 |

| Valore in PR2 |

FFh |

FFh |

FFh |

3FH |

1Fh |

17h |

| Massima risoluzione (bit) |

10 |

10 |

10 |

8 |

7 |

6.58 |

Nel caso in cui il Duty Cycle del PWM sia stato impostato di valore

maggiore del periodo il pin CCPx non cambierà stato.

Nei dispositivi a 28 pin è disponibile la funzione Enhanced dell'

auto-shutdown per il modulo CCP1, ma non per il

CCP2. Nei dispositivi a 40/44

pin le funzioni Enhanced complete sono disponibili per entrambi i moduli CCP.

Setup del PWM

Per disporre della funzione PWM occorrono i seguenti passi :

- impostare il periodo voluto per il PWM scrivendo PR2

- impostare il duty cycle scrivendo il registro CCPRxL e i bit

CCPxCON<5:4>

- stabilire il pin CCPx di uscita del segnale PWM e configurarlo come

uscita con il relativo TRIS

- stabilire il valore del prescaler del timer2, quindi abilitare il timer

con T2CON

- configurare il modulo CCP per il funzionamento in PWM

I registri interessati al PWM

Il foglio dati riporta come al solito un elenco dei registri che sono

interessati dalle operazioni del modulo CCP per le operazioni di PWM.

Il fondo bianco delle celle della Tab.15-3 identifica quali registri e bit

vanno considerati quando si affronta la programmazione (mentre le celle con

fondo grigio indicano bit o registri non interessati).

La gestione dei bit dei registri PIR/IPIR/PIE

per l' interrupt riguarda il Timer2 e sarà considerata dove necessaria,

sempre ricordando che i flag dei registri PIR

sono testabili anche in polling e vanno azzerati da programma quando

necessario.

La collocazione dei flag e dei bit nei registri suddetti indica che gli

interrupt di Timer2 fanno parte del gruppo dei periferici e la loro chiave di

abilitazione, nel caso di interrupt senza priorità, è il bit PEIE

di INTCON.