Il Baud Rate generator

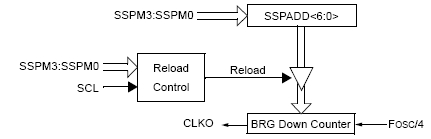

Nel modo Master un baud rate generator (BRG) è disponibile per

produrre il clock della comunicazione.

Il valore di questa frequenza è programmabile scrivendo i 7 bit meno

significativi di SSPADD.

Va osservato che:

- la funzione di generazione del clock è riservata ai Master

sul bus, sia quando trasmettono che quando ricevono.

- Pertanto SSPADD ha lo scopo di permettere la

programmazione del Baud Rate quando MSSP è

selezionato come Master.

- In modalità Slave, una periferica I2C NON

genera il clock. Quindi, quando MSSP è programmato in uno

dei modi Slave, la funzione di Baud Rate Generator

non è presente.

- Però, per lo Slave, lo stesso registro SSPADD

assume la funzione di contenere l' indirizzo attribuito allo

Slave, nelle modalità descritte più avanti.

|

Ogni volta che viene effettuata una scrittura di SSPBUF, il baud rate

generator inizia il suo conteggio.Il BRG è un count down ed è

decrementato 2 volte per ogni ciclo di istruzione (Tcyc).

Una volta che l' operazione in corso è completata, il clock viene arrestato e

SCL rimane nell' ultimo stato in cui si trovava.

E' possibile leggere e scrivere il registro SSPADD in ogni momento.

La possibilità di scrittura è utile in quanto il valore contenuto nel

registro viene passato al BRG ogni qual volta esso deve iniziare un conteggio,

per cui è possibile cambiare la frequenza del clock durante il funzionamento,

ad esempio per comunicare con una periferica più veloce o più lenta di

quanto attribuito genericamente al bus, oppure per effettuare configurazioni

automatiche del Master.

La sorgente del BRG è il clock principale Fosc.

Il valore della frequenza dipende dalla relazione:

baud_rate = Fosc 7 [ 4 * (BRG+1)]

dove BRG è il valore scritto in SSPADD, ovvero:

BRG = (Fosc / (4 * baud_rate) ) -1

La seguente tabella presenta alcuni esempi delle frequenze ottenibili,

mettendo in relazione il clock principale con il baud rate generato per la

comunicazione seriale.

Fosc

[MHz] |

BRG

[hex] |

baud_rate

[kHz] |

| 40 |

0x18 |

400 |

| 0x1F |

312.5 |

| 0x31 |

200 |

| 0x63 |

100 |

| 32 |

0x13 |

400 |

| 0x27 |

200 |

| 0x4f |

100 |

| 16 |

0x09 |

400 |

| 0x0C |

308 |

| 0x27 |

100 |

| 10 |

0x09 |

400 |

| 0x13 |

200 |

| 0x27 |

100 |

| 8 |

0x04 |

400 |

| 0x09 |

200 |

| 0x13 |

100 |

|

4

|

0x00

|

1 MHz

|

|

0x02

|

333

|

| 0x04 |

200 |

| 0x09 |

100 |

Avendo BRG disponibili solo 7 bit, il numero massimo impostabile sarà

0x7F

(127 decimale).

Va notato che l' interfaccia non è perfettamente conforme alla specifica I2C per la frequenza di 400 kHz (o 333 kHz e 1MHz), ma può essere utilizzata

con un attimo di attenzione e verifica sull' applicazione.

Il BRG e la logica di controllo relativa hanno anche lo scopo di fornire le

temporizzazioni necessarie durante la gestione delle condizioni. In

particolare, temporizza gli impulsi del clock, la durata delle condizioni, le

scansioni dei livelli del bus per individuare condizioni imposte e stati di

conflitto.

Inoltre, il

BRG in modo Master supporta la sincronizzazione del clock necessaria alle

operazioni di arbitraggio nei sistemi multi-Master.

Sul clock sono possibili due funzioni speciali:

- il clock stretching , riservato agli Slave

- l' arbitraggio del clock, indispensabile nei sistemi

multi-Master

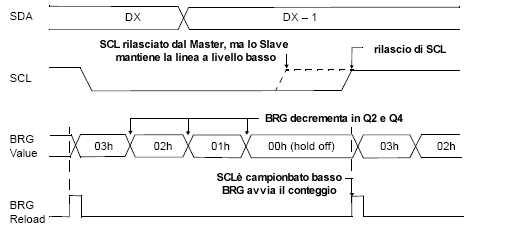

Arbitraggio del clock

L' arbitraggio del clock è una funzione specifica del Master ed è

utilizzata per la sincronizzazione nei sistemi multi-Master.

Si verifica quando il Master, nel corso di uno scambio di dati o delle

condizioni di Restart o Stop, rilascia il pin SCL (che va a livello alto).

Quando il pin SCL è rilasciato, il Baud Rate Generator (BRG) sospende il conteggio

per tutto il tempo in cui il pin SCL è campionato alto. Quando SCL viene campionato alto, il generatore di baud rate è

ricaricato con il contenuto del registro SSPADD <6:0> e

inizia il conteggio. Questo assicura al livello alto di SCL al minimo il tempo

di un periodo di BRG nel caso in cui la linea del clock è tenuta bassa da un dispositivo esterno.

Il diagramma seguente esemplifica i segnali relativi:

Clock Stretching

Il clock stretching è una funzione tipica della modalità Slave.

E'

l' unica situazione in cui lo Slave può manipolare la linea del clock.

Un allungamento (stretching) del tempo di clock ha lo scopo di dare allo

Slave più tempo per sistemare il dato ricevuto o per preparare quello da

trasmettere.

In modalità Slave, sia a 7 che a 10 bit, è possibile implementare

lo stretching del clock automatico durante una sequenza di trasmissione. Il

bit SEN (SSPCON2 <0>) = 1 permette che il clock sia esteso: la linea

SCL

sarà tenuta a livello baso dallo Slave alla fine di ogni blocco di dati

ricevuti. Questo permette allo Slave di avere più tempo a disposizione per il

trattamento del dato ricevuto, rallentando la trasmissione del Master.

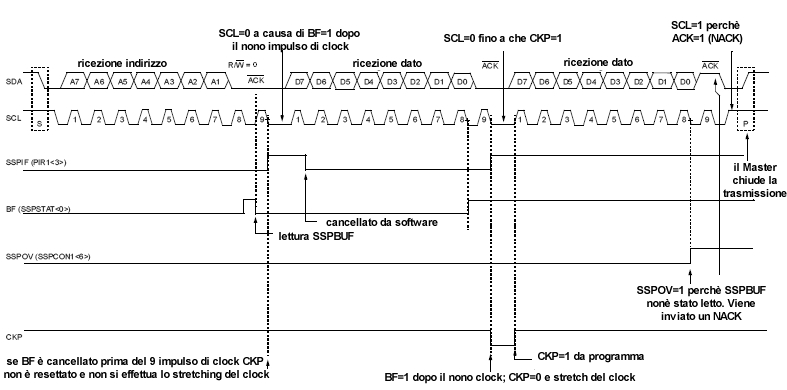

Clock stretching in ricezione

In modalità di ricezione Slave con indirizzo a 7 bit, sul fronte di discesa del

nono impulso di clock, alla fine della sequenza ACK, se il BF è a

1, il bit CKP nel registro SSPCON1 è automaticamente

azzerato, costringendo l'uscita SCL a livello basso.

Per rilasciare la linea occorre che il bit CKP sia azzerato da programma.

Il bit CKP deve essere impostato a 1 da programma prima del la ricezione.

Tenendo la linea SCL a livello basso, l'utente ha il tempo di servire

l' interrupt del modulo MSSP o, comunque, leggere il contenuto di SSPBUF prima

che il Master avvii la trasmissione del dato successivo. Questo consentirà di evitare

overflow del buffer e sospensioni indesiderate della comunicazione.

Va notato che se SEN=1, il che abilita il clock stretching

automatico, occorre una particolare attenzione nel programma di gestione per

cancellare le condizioni di stretching, che, altrimenti, terrebbero

bloccato il bus.

Va notato, inoltre, che, anche se SEN=1, il che abilita il clock

stretching automatico, dove non è necessario può essere evitato:

- se l'utente legge il contenuto di SSPBUF prima che del fronte di discesa del

nono impulso di clock

orologio nono, il bit BF viene azzerato e il bit CKP non verrà cancellato;

in questo modo non si effettua lo stretching del clock (che non

sarebbe necessario, in quanto il dato ricevuto è già stato

letto).

- Il bit CKP può essere imposto a 1 dal software indipendentemente dallo stato del bit

BF per cancellare comunque lo stretching. L' utente deve fare attenzione,

però, a cancellare il bit BF (e SSPIF) prima della prossima

ricezione al fine di evitare una condizione di overflow (SSPOV=1)

che abortirà la comunicazione.

|

Nel modo Slave con indirizzo a 10 bit, durante la ricezione dell'

indirizzo lo stertching del clock avviene automaticamente, ma CKP non va a

zero. Lo stretching è iniziato se il bit è UA è a 1 dopo il

nono impulso del clock.

Ricordiamo che UA=1 dopo aver ricevuto il byte alto dell' indirizzo a

10 bit e questo indica la necessità di aggiornare SSPADD con il valore

della parte bassa dell' indirizzo. Inoltre UA =1 dopo la ricezione di questo

secondo byte, per richiedere l' aggiornamento di SSPADD in modo che sia

pronto per una futura ricezione.

La linea SCL viene rilasciata dallo Slave al momento di aggiornamento

dell' aggiornamento di SSPADD.

Lo stretching si verificherà, poi, su ogni ricezione di dati come descritto

per il modo a 7 bit..

Clock stretching in trasmissione

In modalità Slave di trasmissione, con indirizzo a 7 bit, il clock

viene esteso, portando CKP = 0 dopo il fronte di discesa del nono

impulso del clock.

Questo si verifica indipendentemente dello stato del bit SEN, ma solo se

BF=0.

L'utente deve settare il bit CKP prima della trasmissione.

Tenendo la linea SCL a livello basso, si blocca il bus, ampliando il

tempo di servizio della trasmissione e il caricamento dei dati in SSPBUF

prima che il Master possa avviare un' altra trasmissione con il suo ACK.

Il diagramma esemplifica la situazione dei segnali:

In modalità Slave di trasmissione, con indirizzo a 7 bit, il clock

stretching è controllato durante la ricezione dei 2 byte di indirizzo dallo stato del bit

UA,

esattamente come nel modo di ricezione Slave a 10 bit.

I primi due bytes di indirizzo sono seguiti da un terzo indirizzo che contiene il

byte alto e il bit R / W =1 (richiesta di lettura dallo Slave, che, quindi,

dovrà trasmettere dati).

Dopo il secondo aggiornamento di SSPADD, il bit UA non viene più settato; il modulo è ora configurato in

modalità di trasmissione e lo stretching del clock è controllato dal flag BF come nella modalità

Slave

a 7 bit.

Va notato che:

- il bit R/W del primo byte di indirizzo è a 0 per scrivere il secondo

byte di indirizzo.

- il bit R/W del terzo byte di indirizzo è a 1 per indicare la richiesta

di invio dati.

Nell' esempio del diagramma qui sopra, il Master chiude la trasmissione di

dati dello Slave con uno Stop (P).

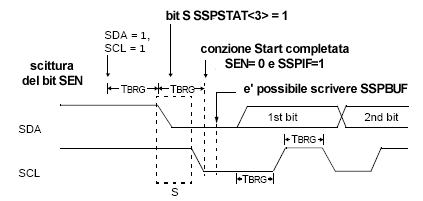

Temporizzazioni della condizione di Start.

Tutte le operazioni di generazione della condizione di Start sono

realizzate dal modulo MSSP in modo automatico.

All''utente è demandata la gestione della logica del protocollo e della

risoluzione di eventuali situazioni anomale.

Abbiamo visto che per avviare la condizione di Start, l' utente

porta a 1 il bit SEN (SSPCON2<0>).

Vengono campionati

SDA e SCL e se sono entrambe a livello alto si suppone

che il bus sia idle. Il baud rate generator viene caricato con il valore

contenuto in SSPADD<6:0> e inizia il conteggio.

Se SCL e SDA sono campionate a livello alto quando il BRG ha esaurito il

conteggio, il pin SDA viene portato a livello basso. Questo intervallo di

tempo ha lo scopo di verificare l' effettivo stato idle del bus.

L' azione di portare a livello basso SDA con SCL a livello alto fa si che il

flag S (SSPSTAT<3>) sia portato a 1. Subito di seguito, il

BRG

viene ricaricato e riparte il conteggio. Quando BRG ha esaurito il tempo,

il

bit SEN viene automaticamente cancellato e il bit SSPIF viene settato

Se all'inizio della condizione di avvio, i pin SDA e SCL sono campionati a

livello basso o se, durante la condizione di avvio, la linea SCL è campionata

a livello basso prima che la linea SDA sia portata a livello basso, questo

indica che c'è una collisione sul bus con un altro dispositivo che sta

trasmettendo. Quindi il Bus Collision Interrupt Flag, BCLIF, è portato a 1, la condizione di

Start viene interrotta e il modulo I2C passa in stato di inattività.

Se l'utente scrive il SSPBUF quando una sequenza di avvio è in corso, il

flag WCOL viene portato a livello 1 e la scrittura non si verifica, lasciando

invariato il contenuto del buffer.

Da notare che, siccome non è consentito accodare eventi, ma occorre

attendere la fine di quello in corso prima di comandare il modulo

MSSP per un'

altro evento, la scrittura dei i 5 bit inferiori di SSPCON2 è disattivata fino a quando la condizione di

Start è stata eseguita completamente.

Possiamo osservare le funzioni specifiche dei flag:

- SEN: è l' "interruttore" che genera lo Start,

portandolo da programma a livello 1.

Ma è anche un indicatore, in quanto torna automaticamente a zero quando

l' evento è completato.

- S: questi flag indica che sul bus è stata verificata una

condizione di Start. Ricordiamo che i pin sul bus I2C hanno contemporaneamente funzione di uscita open drain e di ingresso Schmitt

trigger

- SSPIF: il flag indica il completamento dell' operazione con la

possibilità, se abilitato, di chiamare un interrupt.

Non viene cancellato automaticamente, ma va cancellato da programma,

proprio perchè occorre che il programma gestisca le fine dell' evento

concatenando il successivo. Inoltre, da modo di applicare una gestione in

interrupt, dove il processore, una volta lanciato il comando della

condizione, può svolgere altre attività.

- WCOL: indica un errore nella gestione della comunicazione, dove

si è cercata di avviare una operazione mentre la precedente era ancora in

corso.

- i flag di SSPCON2 hanno proprio lo scopo di evitare questo

errore: nel momento in cui uno di essi è settato, il modulo MSSP non è

libero di accettare un nuovo comando.

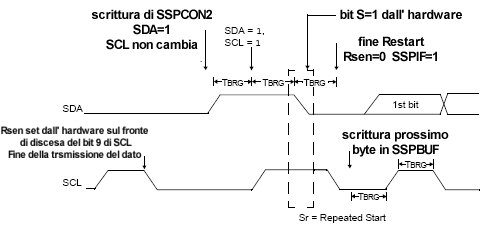

Temporizzazioni della condizione di Restart.

Tutte le operazioni di generazione della condizione di Restart sono

realizzate dal modulo MSSP in modo automatico.

All''utente è demandata la gestione della logica del protocollo e della

risoluzione di eventuali situazioni anomale.

Abbiamo visto che per avviare la condizione di Restart, l' utente

deve portare a 1 il bir RSEN (SSPCON2<1>). Come per la condizione di Start, il bus deve essere

idle.

Quando RSEN viene programmato alto, la linea SCL va a livello basso e lo stato

della linea è campionato. Se SCL è andato a livello basso, il BRG inizia il

conteggio. SDA resta a livello alto per un conteggio al cui termine la linea

viene campionata: se si trova a livello alto, SCL viene rilasciata e va anch'

essa a livello alto a causa dei pull-up.

Ancora SCL viene campionato e se

trovato a livello alto, il BRG viene ricaricato: SCL e SDA sono campionate per

un periodo del conteggio e devono risultare entrambe a livello alto. Questo

viene seguito dall' invio a livello basso della linea SDA per un periodo di

conteggio del BRG, durante il quale SCL resta a livello alto. La sequenza,

quindi, è composta da uno Start e da uno Stop.

Al termine, il bit RSEN viene cancellato automaticamente e il BRG non viene

ricaricato, lasciando SDA a livello basso, impedendo ad altri dispositivi di

accedere al bus. Come per la condizione di Start, il bit S (SSPSTAT<3>)

viene settato e, al momento del time out di BRG, viene settato anche il bit

SSPIF.

Come per gli altri eventi, occorre attendere la fine della condizione prima

di iniziare un nuovo evento. Quindi, se RSEN è stato settato mentre qualsiasi altro evento è in corso, non avrà effetto.

Si verifica una collisione sul bus durante la condizione di Restart se:

- SDA è campionato basso quando SCL va da livello basso a livello alto.

- SCL va basso prima che SDA vada basso. Ciò potrebbe indicare che un altro

Master sta tentando di trasmettere un dati a livello alto.

Immediatamente dopo il settaggio del bit SSPIF, l' utente può scrivere l'

indirizzo dello Slave da chiamare in SSPBUF, nel modo a 7 bit, oppure la prima

parte dell' indirizzo a 10 bit. In ogni caso, dopo la trasmissione di un byte

e la ricezione dell' ACK corrispondente, l' utente può far seguire ulteriori

bytes di dati.

Come per le altre condizioni, non è consentito accodare eventi, ma occorre

attendere la fine di quello in corso prima di comandare il modulo MSSP per un'

altro evento e la scrittura dei i 5 bit inferiori di SSPCON2 è disattivata fino a quando la condizione di

Restart è stata eseguita completamente.

Se l'utente scrive il SSPBUF quando una sequenza di avvio è in corso, il

flag WCOL viene portato a livello 1 e la scrittura non si verifica, lasciando

invariato il contenuto del buffer.

Temporizzazioni della

sequenza di

ACK.

Tutte le operazioni di generazione della condizione di ACK/NACK sono

realizzate dal modulo MSSP in modo automatico.

All''utente è demandata la gestione della logica del protocollo e della

risoluzione di eventuali situazioni anomale. In particolare, la presenza di

situazioni di overflow o errori nella gestione del modulo fanno si che esso

generi un NACK invece di un ACK.

Come abbiamo visto

per le altre condizioni, anche per la generazione dell' ACK il modulo MSSP

fornisce un completo supporto hardware che per

la gestione del bus e le corrette

temporizzazioni e l' avvio della condizione si riduce al settaggio di pochi bit.

Di nuovo, resta all' utente la gestione della struttura logica

connessa e, in particolare, la necessità di verificare il completamento della

condizione precedente prima di avviare l' ACK. In particolare, se l' utente

cerca di scrivere SSPBUF prima del completamento della sequenza di ACK, il flag

WCOL viene settato e la scrittura sul buffer non ha effetto.

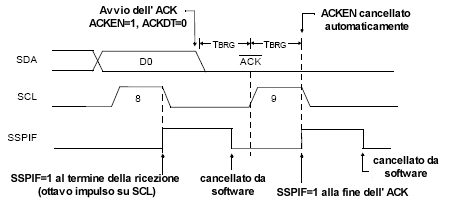

Quando il bit ACKEN viene settato,

SCL viene mandata a livello basso, mentre il contenuto del

bit ACKDT viene copiato su SDA.

In sostanza, dato che ACK e NACK hanno una identica struttura, ma si

differenziano solamente per il valore su SDA, la funzione dei due bit

è semplice:

| bit |

funzione |

| ACKEN = 1 |

avvia la sequenza ACK o NACK |

| ACKDT = 0 |

invia un ACK sulla linea SDA |

| ACKDT = 1 |

invia un NACK sulla linea SDA |

Occorrerà quindi impostare ACKDT prima di ACKEN.

Il BRG conta un ciclo, dopo di che SCL viene rilasciata a livello alto. Se

SCL viene campionata a livello alto, il BRG conta un'altro ciclo, quindi

abbassa SCL, generando il nono bit del clock.

ACKEN viene cancellato automaticamente alla conclusione della condizione,

segnalando alla CPU che il modulo MSSP è libero per accettare un ulteriore

comando. SCL è a livello basso, mantenendo impegnato il bus.

Il diagramma rappresenta la sequenza di ACK. Identica è quella di NACK,

solamente la linea SDA è a livello 1.

il flag SSPIF viene settato alla conclusione della ricezione (dopo l' ottavo

impulso di clock) e alla fine della sequenza di ACK. In entrambi i casi va

cancellato da software.

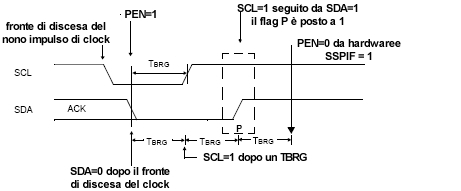

Temporizzazioni della condizione di

Stop.

Tutte le operazioni di generazione della condizione di Stop sono

realizzate dal modulo MSSP in modo automatico.

All'utente è demandata la gestione della logica del protocollo e della

risoluzione di eventuali situazioni anomale.

ACK e NACK non terminano la comunicazione, in quanto n on rilasciano il

controllo del bus (mantenendo SCL a livello basso).

Per terminare la comunicazione e rendere libero il bus occorre generare una

condizione di Stop.

Come abbiamo visto

per le altre condizioni, anche per la generazione dello Stop il modulo MSSP

fornisce un completo supporto hardware che per

la gestione del bus e le corrette

temporizzazioni e l' avvio della condizione si riduce al settaggio di un bit,

ma, di nuovo, occorre ricordare che resta all' utente la gestione della struttura logica

connessa agli eventi.

La condizione di Stop viene

avviata scrivendo a 1 il bit PEN (SSPCON2< >).

Alla fine di una trasmissione o ricezione di dati la linea SCL è a livello

basso dopo il fronte di discesa del nono impulso di clock.

Se PEN viene programmato a 1, il modulo MSSP porta a livello basso la linea

SDA.

Quando questa linea viene campionata a livello basso, il BRG viene avviato ed al

termine del ciclo la linea SCL è rilasciata, ovvero va a livello alto. Il

BRG

effettua un altro ciclo di conteggio e viene rilasciata anche la linea

SDA. Dopo

un ulteriore conteggio di BRG l' evento di Stop è concluso e il bit PEN viene

cancellato automaticamente.

Il flag SSPIF viene portato a uno

al termine della condizione; va cancellato da software.

Contemporaneamente il flag P va a 1.

Come per le condizioni precedenti,

se

l' utente cerca di scrivere SSPBUF prima del completamento della sequenza di

ACK,

il flag WCOL viene settato e la scrittura sul buffer non ha effetto.

|