Firmware controlled Master

A riguardo di questa modalità il foglio dati indica laconicamente che è a carico dell' utente la gestione

del protocollo partendo dai segnali di Start e Stop. Può venire in aiuto il

documento DS31016A, relativo ai Mid-range.

In sostanza, parrebbe che il modo di funzionamento come Master controllato dal firmware

sia una situazione di emulazione del vecchio modulo SSP, che, in I2C,

non aveva la funzione di Master. Per ottenerla occorreva scrivere un

po' di righe di programma, come esemplificato dall' AN-554.

Il funzionamento è supportato dalla generazione di interrupt al rilevamento dello

Start e

dello Stop.

Il controllo del bus può essere preso quando il bit P=1, o il bus è inattivo.

Una gestione firmware è sostanzialmente l' elaborazione di un bit-banging,

dove la generazione dei segnali fa capo esclusivamente ad una serie opportuna

di istruzioni. Così, iIn modalità master le linee SCL e SDA sono manipolati

de-selezionando

il corrispondente TRIS.

Il livello di uscita è sempre basso, indipendentemente dal valore in PORTC. Così, quando la trasmissione

dati deve inserire un bit a 1, si deve portare il bit TRIS di SDA come input,

in modo da rilasciare la linea a causa dell' alta impedenza dell' ingresso.

Per ottenere lo 0 si azzera il bit del PORT e il bit di TRIS. Lo stesso per la

linea SCL.

Nel caso del supporto del modulo MSSP, le operazioni saranno demandate al

modulo stesso.

I seguenti eventi faranno sì che il flag SSPIF di interrupt vada a 1 (interrupt

dal modulo SSP se abilitato):

- condizione Start

- condizione Stop

- trasferimento completato dei dati trasmessi / ricevuti

Avendo a disposizione il modulo MSSP con funzioni di master

supportate interamente, non c'è alcuna ragione per configurare la

modalità firmware controlled.

Funzionamento in stato di SLEEP.

Effetti del Reset.

In modalità Sleep, il modulo I2C può ricevere indirizzi o dati e, quando

un indirizzo o trasferimento di byte è completato, riattivare il processore dallo

sleep (se l'interrupt di MSSP è abilitato).

Un reset disabilita il modulo MSSP e termina il trasferimento di corrente,

rilasciando il bus.

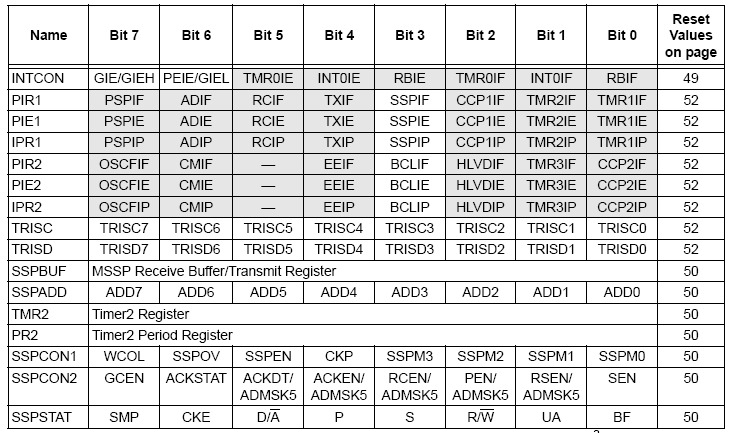

I registri interessati alla comunicazione I2C.

Il foglio dati riporta come al solito un elenco dei registri che sono

interessati dalle operazioni del modulo MSSP per le operazioni I2C.

Il fondo bianco delle celle identifica quali registri e bit vanno considerati

quando si affronta la programmazione (mentre le celle con fondo grigio indicano

bit o registri non interessati).

La gestione dei bit dei registri PIR2/IPIR2/PIE2

sarà considerata dove necessaria, sempre ricordando che i flag dei registri PIR

sono testabili anche in polling e vanno azzerati da programma quando necessario.

La collocazione dei flag e dei bit nei registri suddetti indica che gli

interrupt fanno parte del gruppo dei periferici e la loro chiave di

abilitazione, nel caso di interrupt senza priorità, è il bit PEIE

di INTCON.

I2C e interrupt

Due flag identificano la condizione di interrupt del moduli MSSP. Il primo

flag interessa sia le operazioni come Master che come Slave ed è:

- SSPIF PIR1<3> questo bit va a 1 nelle condizioni

viste durante le descrizioni precedenti..

Va cancellato da programma.

Prima di abilitare l' interrupt di MSSP è opportuno cancellare questo flag per

evitare false chiamate.

Per il resto, la gestione dell' interrupt è analoga a quella degli altri

moduli; sono presenti:

- SSPIE PIE1<3> a livello 1 abilita l' interrupt di MSSP

- SSPIP IPIR1<3> a livello 1 attribuisce la priorità

alta all' interrupt di MSSP, se

IPEN RCON<7> è abilitato

Essendo un interrupt periferico, richiede l'

abilitazione sia di GIE/GIEH che di PEIE/GIEL.

Il secondo flag è interessa solo le operazioni come Master in bus

multi-Master:

- BCLIF PIR2<3> questo bit va a 1 nelle condizioni

di collisone sul bus.

Va cancellato da programma.

Prima di abilitare l' interrupt di MSSP è opportuno cancellare questo flag per

evitare false chiamate.

Per il resto, la gestione dell' interrupt è analoga a quella degli altri

moduli; sono presenti:

- BCLIE PIE2<3> a livello 1 abilita l' interrupt di MSSP

- BCLIP IPIR2<3> a livello 1 attribuisce la priorità

alta all' interrupt di MSSP, se

IPEN RCON<7> è abilitato

Anche questo è un interrupt periferico e richiede l'

abilitazione sia di GIE/GIEH che di PEIE/GIEL.

|