Il RESET

Dobbiamo spendere qualche parola anche su questa funzione, propria di tutti

i sistemi a microprocessore e micro controller, perchè non è semplice come

si può pensare e, nel caso dei PIC Baseline, assume una importanza

particolare.

Per il PIC12F510 il reset può essere generato da varie fonti:

- Power-on Reset (POR)

- livello basso su MCLR durante il funzionamento normale

- livello basso su MCLR durante la condizione di Sleep

- WDT Time-out durante il funzionamento normale

- WDT Time-out durante la condizione di Sleep

- Wake-up dalla condizione di Sleep per cambio di stato di un pin

- Wake-up fdalla condizione di Sleep per cambio di stato del comparatore

Va ricordato che questi Baseline non hanno una gestione di interrupt e vaie

condizioni, come il cambio di stato dei pin o il timeout del WDT generano un

reset. Ne deriva la necessità di discriminare la causa dei vari reset: tutti

riportano il PC al vettore di reset, ma in ogni caso i flag dello STATUS si

trovano in condizoni diverse. Dall' analisi di questi flag si può capire

quale è la causa.

Va ricordato anche che la condizione di reset posiziona vari bit dei

registri SFR nei valori di default.

Da questa tabella possiamo rilevare come i default al POR e dopo un altro

tipo di reset possano essere differenti.

in particolare, si noterà che alcuni biti non vengono modificati dal reset

diverso da POR (u nella tabella), mentre altri, come in OPTION

e TRISGPIO, vengono nuovamente caricati con

i default. Altri registri, come ADCON0 sono

modificati parzialmente.

Per quanto riguarda 16F506, la situazione è analoga, con il solo

aumento del numero dei registri.

Un ulteriore particolare che può essere utile conoscere è questo: i

Baseline non dispongono di timer di power on (PWRT) programmabile, ma hanno

comunque un timer, detto DRT, che inserisce un periodo di wait dal rilascio

del reset da parte del modulo di POR integrato al momento in cui viene

rilasciato il reset generale del microcontroller.

DRT opera in dipendenza di un free running on-chip oscillator, diverso da

INTOSC.

|

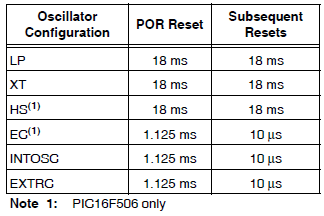

DRT mantiene il PIC in reset per un determinato periodo, come indicato nella

tabella a lato.

Il ritardo generato da DRT non ha una elevata precisione e può

variare a causa di VDD, della variazione di temperatura e dele

tolleranze di lavorazione dei chip. |

Il ritardo introdotto dopo l' arrivo della Vdd minima permette ad essa di

assestarsi e agli oscillatori di stabilizzarsi.

Infatti, oscillatori esterni, basati su cristalli o risonatori ceramici,

richiedono un certo tempo dopo l'accensione per stabilizzare la frequenza

generata, tempo maggiore di quello richiesto da una rete RC.

|

MCLR può essere utilizzato solamente nel caso in cui si applichi

una rete RC esterna se si intende generare ritardi maggiori al POR.

Quindi, una eventuale azione su MCLR ha come scopo solamente il reset

indotto da un comando esterno (pulsante) o per allungare il ritardo

iniziale prodotto dal contatore DRT. |

Occorre avere ben chiaro che il reset all' arrivo della tensione (POR) non

ha nulla a che fare con il reset prodotto da un livello basso applicato sul

pin MCLR.

POR è generato

in maniera indipendente da un modulo interno che dipende dal valore della Vdd.

Quale è lo scopo di MCLR, allora?

Semplicemente quello di azionare il modulo interno di reset con un livello basso, proveniente dall' esterno del chip, applicato al pin.

Quindi, se non dovete resettare il micro dall' esterno, MCLR NON HA ALCUNA UTILITA', nè funzione.

MCLR potrà rivelarsi necessario in alcuni casi particolari:

-

sincronizzare il reset del micro con altre funzioni, ad esempio, una periferica esterna che richiede di aver completato il suo reset prima di poter essere utilizzata. In questo caso è inutile che il micro tenti accessi prima di questo tempo. Per sicurezza, il suo reset dipenderà dal completamento di quello della periferica.

-

disponibilità di un reset già presente in un sistema complesso dove interagiscono più microcontroller o microprocessori e in cui occorre una sincronizzazione, spesso concomitante con un clock comune.

-

utilizzo di un reset supervisor esterno, che mantiene con sicurezza a livello basso il pin MCLR fino a che la tensione non è stabilizzata ad un valore preciso (MCP100, MCP809, ecc)

-

necessitare di un arresto di sicurezza che blocchi il processore su un comando di emergenza proveniente dall' esterno, dove non è possibile togliere la tensione di alimentazione

|

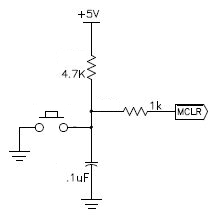

La più classica applicazione su MCLR è il pulsante di

RESET: premendolo, si porta il livello di MCLR a 0, collegandolo alla Vss.

In questo caso il condensatore ha anche una funzione anti rimbalzi.

Si deve ricordare che il debounce di un pulsante con una rete RC è valido solamente se il tempo dipendente da RC è maggiore di quello dei rimbalzi, il che può richiedere anche 5-10ms addizionali nell' avviamento del microcontroller. Inoltre, la tensione di carica del condensatore non è lineare e richiede, per un punto di intervento preciso, almeno uno schmitt trigger: fortunatamente i progettisti hanno considerato questo e l' ingresso MCLR è appunto di questo genere.

|

Di conseguenza, questi chip con un basso numero di pin consentono di

escludere la funzione MCLR, dove essa non servisse, ed utilizzare il pin come

ingresso digitale GP3.

I Baseline non hanno un modulo BOR, che rileva le situazioni di

abbassamento della tensione di alimentazione e questa mancanza può essere

sentita in alcune condizioni.

|

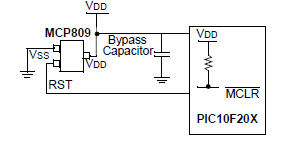

In questi casi sarà utile l' aggiunta di un integrato supervisore

di tensione che possa resettare il processore per abbassamenti della

Vdd al di sotto di un determinato limite di sicurezza.

Perchè questo? Semplicemente perchè il modulo POR agisce SOLO durante la fase di salita della tensione. Quando la tensione scende, il POR non ha alcun effetto. |

Ulteriori

informazioni sul reset sono consultabili qui.

|