La memoria

Riserviamo per ultima una trattazione della memoria, che interesserà principalmente chi vuole capire più a fondo

il funzionamento dei PIC e chi programma in Assembly; meno importante per

chi programma in C o simili.

In questi PIC troviamo due tipi di memoria:

- un' area di memoria FLASH, che comprende la memoria programma

(program memory), la configuration word e il registro ID

- un' area di memoria RAM che comprende la RAM dati e gli SFR

Trovate

qui qualche chiarimento, se occorre, per quanto riguarda il problema di

banchi e pagine.

Memoria programma

PIC16F526 ha un program counter (PC) 11 bit (PC) in grado di indirizzare un programma 2k x 12 (ricordiamo

che l' ampiezza delle istruzione dei Baseline è 12 bit, mentre il bus

dati è a 8 bit - ved. architettura

Harvard).

|

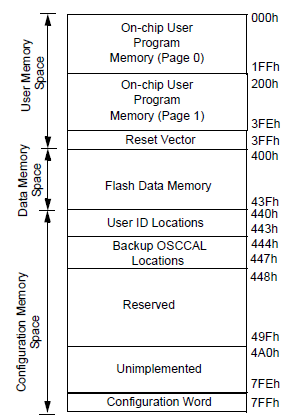

Sono disponibili due pagine di memoria programma (Flash), da

000h a 1FFh e da 200h a 3FFh. disponibili.

Da notare che la mappa indica come vettore di RESET non 000h, ma 3FFh,

che contiene il valore di calibrazione dell' oscillatore interno.

L' area tra 0400h e 043Fh è occupata da una sezione di memoria

Flash che può essere utilizzata durante il programma come area dati.

L' accesso a questa zona si effettua come se si trattasse di una

EEPROM (vedere più avanti).

Le aree successive sono utilizzate per ID, Configuration Word, backup

di OSSCAL o non implementate.o per i PIC, a 0000h.

La locazione 03FFh contiene il valore di calibrazione dell'oscillatore

interno. Questo valore non deve essere cancellato o sovra scritto,

come abbiamo visto nelle pagine dedicate al clock.

Lo stack a 12 bit è di soli due livelli, quindi limita il numero

degli annidamenti di chiamate a subroutine. Non ci sono meccanismi che

indichino un overflow o underflow dello stack; quindi è

responsabilità del programmatore di evitare questi errori.

Nel set Baseline

non ci sono istruzioni di manipolazione dello stack.

|

La memoria FLASH conserva quanti scritto anche al mancare della tensione di

alimentazione, quindi il contenuto delle locazioni da 000h a 043Fh resta

invariato fino a che non viene volontariamente cancellato e/o riscritto.

Memoria RAM

La memoria di dati è composta di registri o byte in RAM, ovvero di memoria

scrivibile e leggibile a volontà, ma che perde quanto contenuto al momento in

cui la tensione scende sotto un valore minimo di mantenimento o viene a

mancare del tutto. Nella stessa area sono implementati i registri di

controllo SFR.

In effetti, Microchip divide i registri in due gruppi funzionali:

- Special Function Registers (SFR)

- e registri di uso generale (General Purpose Register - GPR).

I registri SFR includono TMR0, il Program Counter (PCL), lo

STATUS, i registri di I/O e il file

di indirizzamento indiretto (FSR). Sono SFR anche tutti i

registri utilizzati per controllare la configurazione delle risorse interne.

I registri di uso generale sono la vera e propria RAM dati, sotto il comando delle

istruzioni del programma.

Per il PIC16F526 ci sono:

L' area RAM occupa 4 banchi. Lo schema seguente riporta la

mappa dell' area RAM:

Si può osservare che:

- il Bank0 e il Bank2 replicano gli stessi SFR; così pure il Bank1 e il

Bank3

- la maggior parte degli SFR sono accessibili da tutti i banchi

indistintamente, mentre i registri relativi alla EEPROM sono accessibili

solo dal Bank1-3

Quindi, ad esempio, chiamando il registro all' indirizzo 05h, se ci si

trova nel Banko o Bank2 si accederà a OSCCAL;

se ci si trova nel Bank1 o 3, si accederà a EEDATA.

Per quanto riguarda la RAM dati:

- un' area di soli tre bytes, da 0Dh a 0Fh costituisce l' area comune a

tutti i banchi

- ogni banco dispone di un'area di 16 bytes

Il passaggio tra i banchi viene effettuato agendo sui bit FSR<6:5>:

| FSR<6:5> |

Bank |

| 00 |

0 |

| 01 |

1 |

| 10 |

2 |

| 11 |

3 |

Va considerato che, seppure General Purpose Register e SFR sono

entrambi "RAM", i primi non vanno usati per conservate dati,

poichè sono in relazione con la gestione delle varie funzioni del

processore; solamente i GPR saranno da impiegare come aree di memoria

volatile per i dati.

Possiamo anche notare che i registri TRIS

e OPTION non appaiono nella mappa della memoria in quanto sono SFR speciali a

sola scrittura, accessibili rispettivamente ed esclusivamente con le istruzioni

relative tris e option.

Può essere utile dare uno sguardo anche la tabella riassuntiva degli SFR, in cui

appaiono i valori di default al reset.

La tabella riporta:

- l' indirizzo assoluto del registro nella mappa della memoria RAM

- il nome (label) del registro

- gli mnemonici relativi ai bit

- il valore di default al POR (x indica un valore casuale)

- la pagina del foglio dati dove sono sono descritti nel dettaglio questi

registri

In particolare:

- il bit 5 dello STATUS costituisce lo switch di pagina per accedere alla

parte superiore della memoria programma:

- PA0 = 0 -> primi 512 bytes

- PA0 = 1 -> restanti 512

bytes

- il bit 5 di FSR costituisce lo switch per accedere ai banchi:

- FSR<5> = 0 -> Banco 0

- FSR<5> = 1 -> Banco 0

Queste informazioni riguardano la programmazione Assembly, dove è cura del

programmatore il dirigere il flusso di istruzioni alla giusta

destinazione. Nell' uso di compilatori, invece, è il compilatore che

provvede a commutare banchi o pagine a seconda della necessità.

- Sempre nello STATUS, il bit 7 (RBWUF) va a 1 dopo un reset prodotto dal

wake-up dovuto al cambio di stato dei pin di PORTB e CWUF

a seguito del cambio di stato del comparatore

|