La connessione I2C

I2C

(Inter Integrated Connection) è uno standard per lo scambio dati con una

interconnessione seriale sincrona, studiato da Philips (attualmente NXP) che ne

detiene i diritti. Analogo a I2C è SMBus (System

Management Bus) di Intel, con struttura simile, ma con qualche differenza sulle soglie dei

livelli logici.

Esiste poi un CBUS che però presenta varie differenze anche

hardware. Troviamo

anche costruttori che realizzano dispositivi denominati

genericamente 2-Wire Serial Interface, con una compatibilità I2C.

Comunicazioni del genere I2C sono presenti in molte applicazioni, ad esempio

nell' interfaccia tra schede video e monitor (VGA, HDMI) o per l' accesso

ai serial presence detect (SPD) delle DIMM e altri componenti per sistemi

computerizzati, ecc.

Come dice il nome, si tratta di una connessione tra circuiti integrati,

prevista per collegare vari dispositivi presenti su circuito stampato o all'

interno di una apparecchiatura.

Il sistema include la possibilità di avere più dispositivi sia Master (multi-Master)

che Slave, collegati tra di loro utilizzando solamente due conduttori, uno per

i dati ed uno per il clock.

Siccome sia Master che Slave possono trasmettere e ricevere dati, la linea

dati è bi-direzionale.

E lo è anche il clock, in quanto sarà il

dispositivo in linea in quel momento a comandarlo.

In effetti, secondo la definizione originale del protocollo, sono identificati

i seguenti elementi:

| Transmitter |

il dispositivo che sta inviando dati sul bus |

| Receiver |

il dispositivo che riceve dati dal bus |

| Master |

il dispositivo che inizia e termina un trasferimento

dati.

Il Master è il

dispositivo che può prendere in carico il bus in un dato momento e che sta

generando il clock della trasmissione. |

| Slave |

il dispositivo indirizzato dal Master.

Sono dispositivi Slave quelli che non possono comunicare tra di

loro, ma solo con un Master. |

| Multi Master |

più di un Master che possono cercare di avere il

controllo del bus senza che siano corrotti i messaggi in linea |

| Arbitraggio |

l' operazione che assicura ad un solo Master alla

volta l' accesso al bus |

| Sincronizzazione |

procedura per sincronizzare due o più

dispositivi. |

Siccome I2C è multi-Master,

un dispositivo che opera come Master potrà operare anche come Slave di un

altro Master. I Master sono solitamente dei microcontroller e questo

significa che più microcontroller possono essere collegati al bus e comunicare

sia tra di loro che con eventuali Slave.

Per riassumere, I2C è un sistema seriale sincrono con due linee

bi-direzionali, multi-Master.

- la line dati è chiamata SDA (Serial DAta) e

- la linea del clock è chiamata

SCL (Serial CLock).

|

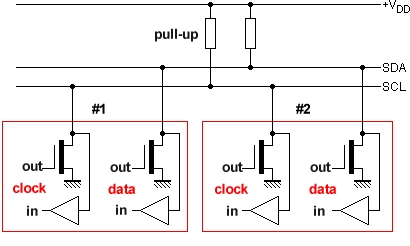

Dovendo consentire accessi bi-direzionali alle linee fisiche di trasporto

del clock e dei dati, ne risulta che la configurazione tipica è costituita da

periferiche con interfaccia open drain, o open collector, "appese" a

linee dotate di pull-up (wired-AND). E' una configurazione single-ended con il riferimento alla

tensione di alimentazione. I vari dispositivi sono semplicemente

aggiunti collegandoli ai due conduttori del bus. |

I pull-up, dunque, non sono opzionali, ma sono indispensabili, in quanto le linee,

se non mandate a livello basso alla chiusura degli open drain, sarebbero ad un

livello logico indeterminato e quindi inaccettabile dagli ingressi di

ricezione.

Questa soluzione circuitale consente di aggiungere (entro i limiti del

collegamento fisico) periferiche al bus senza modifiche, consentendo una

scalabilità verso un numero maggiore di dispositivi. Sono stati

prodotti anche line extender che consentono di superare le brevi distanze costituite da cablaggi all' interno di

una apparecchiatura o anche buffer in grado di portare i segnali fuori di essa. Per contro, la bi-dierzionalità delle linee rende più

complessa la bufferizzazione e l' isolamento galvanico rispetto a bus con

linee mono direzionali.

La soluzione open collector (o open drain) fa si che, quando uno dei

dispositivi manda in conduzione la propria uscita, essa forza a livello basso

la linea (livello

logico zero); nel momento in cui l' uscita si disabilita, la linea viene

riportata a livello alto (livello logico uno) dal pull-up.

La configurazione

ha il vantaggio di non avere in nessun caso conflitti hardware, dato che

nessun

dispositivo può forzare il livello logico alto: al massimo, se due

dispositivi vanno in conduzione nello stesso istante, non si verifica alcuna

sovracorrente, dato che entrambi non sono altro che interruttori in parallelo

e la corrente viene limitata dal pull-up.

Ovviamente il pilotaggio

del bus non può essere effettuato da GPIO generici che tipicamente hanno una uscita puh-pull, come

la gran parte dei pin dei microcontroller: se un dispositivo push-pull sul bus

porta

la sua uscita a livello alto mentre un' altro lo forza a livello basso, si

verifica un corto circuito tra la tensione di alimentazione e la massa

attraverso i semiconduttori di pilotaggio delle uscite.

Dovendo utilizzare questo genere I/O, il livello alto richiederà il passaggio

del pin da uscita a ingresso (ad alta impedenza), lasciando al solo pull-up il

compito di attribuire alla linea il giusto livello alto.

Tuttavia esistono

microcontroller con I/O open drain o programmabili come tali.

Mancando questi

sarà opportuno ricorrere a componenti esterni.

In sostanza, i conduttori del bus possono assumere solo due stati:

- float

high quando nessun dispositivo è in conduzione; la tensione positiva

è assicurata dai pull-up

- driven low

quando un open drain (o open collector) viene chiuso, mandando la linea a

livello basso.

Ovviamente occorre che solamente una unità sia in trasmissione in un dato

istante, dato che se più unità agiscono contemporaneamente portando a

livello basso la linea, non si verificano sovracorrenti, ma il contenuto dell'

informazione va perso. Questo richiede che sia verificato lo stato di linea

libera prima iniziare la trasmissione.

Per questa ragione i dispositivi non invertono la loro direzione a seconda che

siano in trasmissione o ricezione, ma dispongono su ognuna delle linee di uno

switch per la trasmissione (transistor bipolare open collector o MOSFET open

drain) e, contemporaneamente, un gate di ricezione, tipicamente Schmitt

trigger per minimizzare il rumore.

Questa architettura è indispensabile non solo per la verifica dello stato

idle della linea, ma per l' ulteriore ragione che i livelli logici sulle due

linee non costituiscono solo la trama della trasmissione, ma, con particolari

configurazioni, forniscono degli stati che il sistema identifica come

handshake, detti "condizioni", che saranno decritti più avanti.

La comunicazione

si svolge al livello dell' alimentazione dei circuiti integrati, che va

tipicamente dai classici 5V al minimo supportato dai dispositivi collegati, ad esempio

3V, anche se non ci sono teoricamente limiti al valore della Vdd.

Dato che, però, i dispositivi non solo trasmetto in linea, ma anche ricevono

nello stesso tempo, se sullo stesso bus sono collegati dispositivi alimentati a tensioni diverse

occorrerà introdurre traslatori di livello o altri artifici hardware per

adattare i livelli logici, anche se dispositivi recenti hanno ingressi che

supportano una ampia gamma di tensioni.

Su un bus di questo genere non è consigliabile inserire altro che dispositivi

I2C, dato che il cambio di stato delle linee ha funzione

di segnalazione; l' eventuale inserimento di altri dispositivi richiede la

massima cautela.

I2C prevede il supporto per una ampia gamma di frequenze di

clock:

| modo |

data rate |

| standard-mode |

Sm |

100 kbps |

| fast-mode |

Fm |

400 kbps |

| fast-mode plus |

Fm+ |

1 Mbps |

| hig speed mode |

Hs |

3.4 Mbps |

Trattandosi di una comunicazione sincrona con il clock separato dai dati, la

precisione dell' oscillatore è relativa e, al limite, il clock può variare

durante la trasmissione senza perdita del dato, tanto che il protocollo

prevede una azione, detta clock stretching, in cui l' unità in

trasmissione rallenta il clock.

Questo consente di mescolare su uno stesso bus unità differenti come

prestazione e non far dipendere la larghezza di banda solamente da quella più

lenta.

Come è evidente, sul bus potranno comunicare solamente due dispositivi

alla volta in una modalità half-duplex; l' accesso di più periferiche in

trasmissione è controllato ed impedito dai sistemi di handshake, mentre tutti

i dispositivi collegati al bus si trovano sempre e comunque in stato di

ricezione in attesa di essere selezionati con il proprio indirizzo oppure di

entrare in trasmissione come Master nel momento in cui le linee siano libere; lo standard stabilisce sistemi di general call per inviare

particolari messaggi a tutti i dispositivi sul bus contemporaneamente.

Il bus I2C

Philips-NXP ha previsto il bus per collegare ogni genere di

periferica in modo seriale ad uno o più microcontroller che governano un

sistema o una apparecchiatura.

Le applicazioni spaziano dagli apparecchi TV ai personal computer, dagli

strumenti di misura ai sistemi di supervisione di processo.

La pubblicazione UM1024

esemplifica un bus complesso dove sono presenti più microcontroller e una

suddivisione del bus stesso in sezioni attraverso multiplexer e repeater.

Philips ha infatti realizzato una gamma molto ampia di funzioni per I2C

, non solo periferiche come I/O expander e EEPROM, ma anche elementi di

supporto a bus complessi, come multiplexer, repeater, buffer, level translator,

ecc.

|