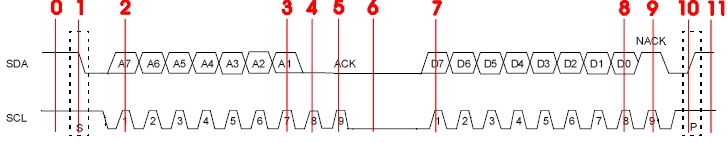

Rivediamo il protocollo

Alla luce di quanto finora detto, possiamo vedere, quindi, con maggior

consapevolezza lo svilupparsi di una

sessione di comunicazione.

| 0. |

Il dispositivo che intende trasmettere, e che diventerà quindi il

Master, verifica che la linea sia idle, ovvero SDA e SCL sia

rilasciati a livello alto. |

| 1. |

Quindi il Master acquisisce il controllo del bus generando la

condizione S-Start. Gli altri dispositivi recepiscono questa

condizione e si pongono in attesa dei dati successivi.

SDA e SCL sono costretti a livello basso. |

| 2. |

Per primo viene inviato un indirizzo. Nell' esempio, 7 bit. Per ogni

bit viene rilasciato SCL, che va a livello alto attraverso il

pull-up. I dati sono validi con SCL = 1 |

| 3. |

Al settimo colpo di clock i bit di indirizzo sono esauriti |

| 4. |

Viene generato un ulteriore impulso di clock per l' ottavo bit, che

contiene l' informazione R/W. Nell' esempio R/W=0.

Tutte le periferiche comparano l' indirizzo ricevuto con il proprio e

quella che lo rileva uguale si predispone per la risposta. |

| 5. |

Un ulteriore impulso sul clock, il nono, serve alla periferica

chiamata per inviare la condizione di ACK, mantenendo SDA a livello

basso. Il Master rileva la condizione. |

| 6. |

Il Master mantiene il controllo del bus |

| 7. |

ed inizia la trasmissione del dato successivo, che si svolge come il

precedente. |

| 8. |

Tutti e 8 i bit del byte dello shift register sono "dato",

per cui occorrono 8 impulsi di clock |

| 9. |

Al nono impulso di clock, la periferica risponde, in questo esempio,

con un NACK, non agendo sulla linea SDA, che resta a livello

alto. |

| 10. |

Quindi il Master chiude la trasmissione generando uno Stop-S. I

dispositivi sul bus rilevano la condizione che avvisa dell' intenzione

del Master di liberare il bus. |

| 11. |

Il Master rilascia il bus, le cui linee si riportano a livello alto,

grazie ai pull-up. Ora un qualsiasi dispositivo potrà assumere il

controllo delle linee. |

Il protocollo, dunque, non è particolarmente complesso: visto alla luce di

quanto finora detto è ragionevole e logico nello sfruttare al massimo le due

linee di trasmissione.

Ma non è neppure semplice, in quanto è necessario che i dispositivi sul

bus identifichino le condizioni, generino i segnali con le giuste

temporizzazioni, ecc. Il tutto con il massimo clock possibile.

Se poi il dispositivo deve supportare ilo clock stretching, occorrerà anche

che il Master verifichi, al rilascio della linea SCL, il suo effettivo stato a

livello alto (e, per lo Slave, sia implementata questa funzione).

Da quanto sopra si deduce che una emulazione software del protocollo è fattibile

utilizzando le istruzioni di un generico microcontroller, privo di modulo

specifico per la comunicazione sincrona, e con I/O altrettanto generici, ma è

ragionevole solamente nell' ambito di un bit-banging.

Implementare il protocollo per ogni aspetto della comunicazione e,

principalmente per una gestione non in polling, richiede risorse e un lavoro

ben più costosi che non la scelta di un microcontroller che disponga del

modulo adeguato. Modulo che, peraltro, è presente nella gran parte dei

prodotti più recenti, che, tra l' altro, avranno costi minori di quelli più

datati.

Inoltre è comprensibile che sia necessario, nell' analisi dello stato

delle linee in attesa delle varie condizioni, una frequenza di lavoro molto

maggiore di quella del clock, sia che si tratti di una soluzione hardware,

sia, e decisamente di più, nel caso si tratti di una soluzione software.

Questa necessità di campionamenti è la causa per cui, anche nei

microcontroller dotati di modulo di comunicazione sincrona, il clock massimo

consentito è solitamente molto minore di quello primario: ad esempio, nei

PIC18F, con Fosc di 40 MHz, il massimo baud rate ottenibile è di 400 kHz,

ovvero 100 volte inferiore.

Ne deriva che emulazioni software, comunque sempre possibili, avranno anche

una prestazione inferiore a quella ottenibile con il modulo adeguato, dove, ad

esempio, l' identificazione delle condizioni non è effettuata da istruzioni,

ma dalla logica hardware del modulo stesso.

Quindi è comprensibile come trasmissioni High Speed a 3.4 MHz richiedano

dispositivi particolari, oltre ad una struttura fisica del bus adeguata a

questa frequenza.

Sarà invece più semplice operare con clock a frequenza minore, dove il 400

kHz rappresenta un valore limite per molte periferiche.

|