Il modulo MSSP come I2C

Nei PIC il modulo MSSP (Master Synchronous Serial Port - port seriale sincrono con

funzione di master) è in grado di svolgere le funzioni di Master e di Slave

per il bus I2C (Inter Integrated Circuit).

Questa funzione di interfaccia con il bus comprende il supporto alla

general call e fornisce una sorgente di interrupt per gli eventi di Start e

Stop, oltre a poter gestire indirizzi a 7 e 10 bit.

Inoltre può essere programmato per interfacciarci al SMBus, che ha

caratteristiche hardware leggermente diverse da I2C.

I2C, introdotto da

Phlips-NXP negli anni '90, è uno dei sistemi

più diffusi di comunicazione seriale sincrona su brevi distanze ed esiste

una ampia gamma di periferiche, tra cui EEPROM, driver per

display, AD e DA converter, RTC, ecc.

Il modulo MSSP dispone di alcuni registri di controllo per I2C,

con cui l' utente

programma le varie funzioni e gestisce la comunicazione. I moduli MSSP delle

varie famiglie di PIC sono analoghi a quello qui descritto, per cui quanto

detto può essere esteso in senso generale.

Da notare che alcuni PIC dispongono di modulo SSP (Synchronous Serial Port)

che si differenzia da MSSP in quanto non supporta il modo Master in I2C.

I2C è un protocollo sincrono, dove l' unità che trasmette sul bus fornisce

il clock.

Ne è possibile anche una emulazione software usando generici I/O e comandandone i livelli al momento appropriato, ma il codice di una tale

emulazione, al di la di un bit-banging tra il microcontroller e una

periferica, non è banale. In particolare se esso deve essere scritto in un modo non-blocking

(ovvero in modo tale da permettere al processore di fare altre cose durante la comunicazione I2C).

Ne risulta che l' uso del modulo integrato fa si che sia decisamente più

semplice il programma dello scambio dati e rende possibile una gestione in

interrupt.

Va notato che il modulo MSSP fornisce un completo supporto hardware

al protocollo

I2C, sia

come Master che come Slave. In particolare, la logica integrata

riconosce automaticamente le condizioni sul bus, genera condizioni con

le dovute temporizzazioni, automatizza la trasmissione e ricezione di

byte nello shift register, gestisce la sincronizzazione del clock e l'

arbitraggio, fornisce flag e interrupt per i vari eventi

significativi.

Però la

risposta ai vari eventi e, in generale, la

logica di gestione della comunicazione I2C

sono carico del software scritto dall' utente. |

I2C

La trasmissione dati tra i dispositivi del bus I2C

avviene su due

conduttori bidirezionali, open collector (o open drain) sostenuti da

pull-up.

- La linea dati è indicata come SDA e che fa capo

tipicamente al pin RC4

- La linea del clock, indicata come SCL, fa capo al pin RC3

Varie pagine con maggiori dettagli sul protocollo e le sue

caratteristiche le

trovate qui.

Il modulo

MSSP può operare come interfaccia

SPI o I2C e i pin dedicati

alla comunicazione sono gli stessi:

| Pin |

Funzione |

Note |

| SPI |

I2C |

SPI |

I2C |

| RC5 |

SDO |

- |

Serial Data Out |

non utilizzato |

| RC4 |

SDI |

SDA |

Serial Data In |

dati - bi direzionale |

| RC3 |

SCK |

SCL |

Serial Clock |

clock - bi direzionale |

| RA5 |

/SS |

- |

Slave Select (negato) - opzionale |

non utilizzato |

Poichè i due bus non sono

compatibili, un singolo modulo SSP potrà operare solo o come SPI o

come I2C. |

Dovendo utilizzare contemporaneamente entrambe le interfacce,

occorrerà scegliere uno dei tanti PIC dotato di due o più moduli

MSSP, oppure

utilizzare il modulo per I2C

ed emulare SPI da software.

Va da se che le possibilità funzionali del modulo sono maggiori di

quello che sarebbe ragionevolmente possibile con una emulazione

software.

| Per la connessione di base non servono altri pin, ma può essere

necessario disporne, in quanto alcune periferiche hanno funzioni

addizionali, come un reset e/o in una uscita di interrupt, che sarà

necessario gestire separatamente dal modulo MSSP. |

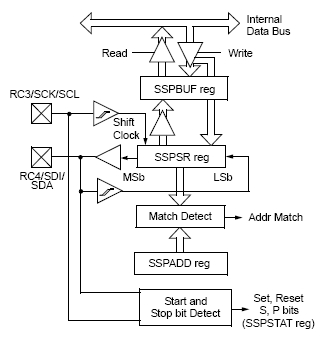

Siccome la comunicazione I2C

è costituita dalla trasmissione sincrona di dati e clock separati, il

prototipo della periferica è, come per SPI, uno shift register.

Però il bus I2C

prevede una gestione di stati di acknowledgement, oltre alla trasmissione

bidirezionale dei dati su un solo conduttore. Inoltre la selezione della

periferica è effettuata con un indirizzo.

Queste condizioni fanno si che la struttura dello shift register di base sia

accompagnata da una complessa logica.

|

Le operazioni di scrittura e lettura non sono effettuate sullo

shift regster SSPSR, ma sul buffer intermedio SSPBUF,

colleganto

con il bus dati interno.

Le condizioni di scrittura o lettura abilitano i buffer che

collegano il registro per l' una o per l' altra operazioneIl

dato ricevuto viene copiato nel registro SSPSR che può essere

comparato con il contenuto del registro SSPADD in cui il

programmatore avrà caricato l' indirizzo attribuito al

microcontroller quando è in modo Slave. Il risultato della

comparazione va ad attivare un flag.

Nel modo Master il registro contiene invece le informazioni relative

al Baud Rate Generator.

A questo proposito dobbiamo ricordare che il clock sul bus è

fornito dall' unità Master che sta trasmettendo in quel momento.

|

Riveste particolare importanza la logica che permette di monitorare

in continuazione lo stato delle linee SDA e SCL e rilevare

automaticamente le condizioni di Start e Stop.

Il clock in trasmissione è derivato dall' oscillatore primario (Fosc/4) e,

per i PIC 18F con clock a 40 MHz può arrivare a 400 kHz, quindi sono eseguibili

trasferimenti dati nei modi standard e fast. E' possibile generare anche un

clock a 1MHz per il modo Fast plus, ma va detto che la documentazione

Microchip indica una non completa aderenza alle specifiche di temporizzazione

di I2C per clock maggiori di 300 kHz. Questo normalmente non crea

alcun problema, dato che i componenti I2C hanno tolleranze

sufficienti per assorbire eventuali differenze su segnali e clock, ma,

sostanzialmente, indica nel modo Standard a 100 kHz il compromesso più

sicuro.

Va comunque tenuto presente che la massima frequenza realmente raggiungibile dipende

dalle caratteristiche del bus e delle periferiche collegate.

Il modo High Speed a 3.4MHz non è eseguibile da parte dell' MSSP

standard,

anche in relazione al fatto che il protocollo, per questa modalità, presenta

differenze rispetto agli altri modi, oltre a richiedere ai pin del bus un

hardware differente.