Gli I/O digitali

Per quanto riguarda le altre funzioni, possiamo iniziare da quella più

semplice, ovvero I/O digitale.

Come I/O digitale si intende che il pin può essere utilizzato come ingresso

per livelli logici, ovvero che possono assumere due valori:

|

1 |

livello

alto |

high

level |

H |

Vh |

| 0 |

livello basso |

low

level |

L |

Vl |

Quindi, con una alimentazione Vdd=5V il livello basso sarà circa uguale a

0V

e quello alto uguale a circa 5V.

In effetti esiste una certa area in cui il

valore è considerato basso (<0.8V) o alto (>2V).

Al di fuori di questi

valori il segnale applicato è irregolare e può essere fonte di errori di

interpretazione da parte del circuito logico di ingresso.

Dati completi sulle caratteristiche elettriche dei pin le trovate nel foglio

dati alla tab. 10-1.

|

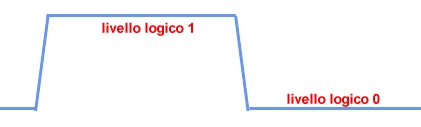

Il passaggio dal livello alto a quello basso si chiama

fronte di

discesa (falling edge). |

|

Il passaggio dal livello

basso a quello alto si chiama fronte di salita (rising edge). |

Le transizioni da un livello all' altro sono spesso utilizzate

per sincronizzare segnali o come indicatori di evento.

Nei PIC i pin sono ingressi a tecnologia CMOS, quindi con alta impedenza e

bassissimo assorbimento di corrente (1uA). Altre informazioni sugli ingressi

digitali dei PIC

le trovate qui.

La funzione di ingresso digitale ci permette di rilevare lo stato di

interruttori, contatti, encoder, linee di comunicazione, ecc.

Analogamente, nell' uso del pin come uscita sarà reso un livello di tensione

maggiore di Vdd-0.7V quando si imposta il pin a livello alto e minore di 0.6V

quando lo si imposta a livello basso. Nei PIC i pin in uscita hanno driver MOS

complementari che possono erogare (source) o assorbire (sink) fino a 25mA. Se

occorre più corrente, si aggiungerà un buffer esterno. Maggiori informazioni

sugli I/O

digitali dei PIC le trovate qui.

La funzione di uscita digitale ci permette di comandare LED, lampade, relays,

motori, display, linee di comunicazione, ecc.

Ingressi e uscite

I pin con funzione di I/O digitale possono, per prima cosa, essere

configurati come linee di ingresso o come linee di uscita (I/O - Input/Output).

Ovviamente non è possibile per un pin svolgere entrambe le funzioni nello

stesso momento!

Dovrebbe essere più o meno noto che i pin in funzione digitale sono

raccolti logicamente in gruppi, detti PORT.

Questi gruppi sono tipicamente composti da 8 bit (8 bit = 1 byte), anche perchè

il bus della memoria dati, che comprende sia la RAM che i registri di

controllo degli I/O (SFR) è a 8 bit.

Nel nostro caso, il piccolo chip ha solo 8 pin, di cui 6 sono utilizzabili

come I/O e che fanno parte di un PORT chiamato GPIO (General Purpose IO).

Nel nostro caso il PORT GPIO ha questo aspetto:

| GPIO |

Bit |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| label |

- |

- |

- |

- |

GP3 |

GP2 |

GP1 |

GP0 |

| pin |

- |

- |

- |

- |

8 |

3 |

4 |

5 |

Essendoci solamente 4 pin validi, i bit 7-4 del registro non hanno alcuna

funzione: leggendoli, si leggerà uno 0 e scrivendoli non si avrà alcun

effetto.

Osserviamo una relazione tra i pin del chip, le label relative alla funzione

digitale e i bit del PORT GPIO.

Ad esempio, il bit 2 del GPIO sarà GP2 e corrisponderà al pin 3 del chip; e

così via.

Teniamo anche presente che al reset il valore di questi bit è casuale.

Nella mappa di memoria dell' area dei registri (area RAM)

GPIO è posto all' indirizzo 06h. Quindi, in valori assoluti,

potremmo scrivere:

6,3

ovvero il bit 3 del registro 6. Ma l' uso di valori assoluti per

identificare le risorse del microcontroller è decisamente contrario allo

scopo dei linguaggi di programmazione. Dal punto di vista del

programmatore, un bit (corrispondente ad un pin) sarà indicato, invece, nella

forma simbolica, ovvero con la sua label; ad esempio, il bit, corrispondente

al pin 4 sarà identificato come GP1.

Per essere precisi, con la forma:

GPIO, GP1

Il livello del pin è applicabile a volontà dal programmatore agendo sui

bit di questo registro oppure, leggendolo, si avrà il livello logico

applicato al pin..

Va tenuto presente che, prima di utilizzare il pin come uscita o come ingresso

occorre configurarlo, attraverso le istruzioni del programma, agendo sul

registro di direzione.

|

Il diagramma a lato rappresenta la struttura semplificata di in pin

di I/O dei Baseline.

Il buffer di uscita è realizzato con una coppia complementare di

MOSFET. Come ingresso, la linea è protetta dalle sovratensioni con

una coppia di diodi.

Il livello applicato all' ingresso è riportabile sul bus dati

attraverso un gate (RD port) che viene aperto dalla lettura del

registro GPIO.

La funzione di uscita è eseguita con i supporto di due latch:

- Il Data Latch conserva il dato scritto in uscita, caricato il

livello imposto sul bus dati alla scrittura del registro GPIO

- il valore conservato nel latch viene passato al buffer di uscita

solamente se il TRIS Latch è stato caricato con 0, scrivendo il

registro TRIS

|

Il Data latch corrisponde al gruppo di bit raccolti nel registro GPIO,

visto sopra.

Il Tris Latch corrisponde ai bit del registro TRISGPIO, del tutto analogo

al precedente. TRISGPIO è una locazione di

memoria RAM a 8 bit. Ognuno dei bit corrisponde ad un pin. Il valore 1 o 0

scritto in quel bit stabilisce la direzione del pin.

Per potere assegnare ai pin la funzione di ingresso o di uscita, si deve

agire su un registro apposito, in questo caso chiamato TRISGPIO,

il quale stabilisce la direzione.

Il nome "tris" è abbreviazione di tri-state

ed è usato qui per indicare il fatto che il pin possa essere programmato come

uscita (con impedenza basssa) o come ingresso (con impedenza molto alta).

Da notare che TRISGPIO non fa parte

della mappa di memoria RAM, in quanto è un registro particolare, a

sola scrittura, la quale è possibile unicamente attraverso una

speciale istruzione tris,

tipica dei Baseline.

Da notare che TRISGPIO non fa parte

della mappa di memoria RAM, in quanto è un registro particolare, a

sola scrittura, la quale è possibile unicamente attraverso una

speciale istruzione tris,

tipica dei Baseline. |

Il registro ha questa struttura:

|

TRISGPIO

|

bit

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

nome

|

-

|

-

|

-

|

-

|

- |

-

|

-

|

-

|

|

funzione

|

- |

- |

- |

- |

W |

W |

W |

W |

|

default

|

- |

- |

- |

- |

1 |

1 |

1 |

1 |

-

bit 7:6 non

utilizzati

-

bit

5 Direzione GP5 : I/O

1 =

ingresso

0 =

uscita

-

bit 4

Direzione GP4: I/O

1 =

ingresso

0 =

uscita

-

bit

3 Direzione GP3 : solo ingresso

1 = ingresso

-

bit 2

Direzione GP2: I/O

1 =

ingresso

0 =

uscita

-

bit

1 Direzione GP1: I/O

1 = ingresso

0 =

uscita

-

bit

0 Direzione GP0: I/O

1 =

ingresso

0 =

uscita

Come per GPIO, essendoci solamente 4 pin validi; gli altri non hanno alcuna

funzione: leggendoli, si leggerà uno 0 e scrivendoli non si avrà alcun

effetto.

Al reset tutti i bit sono forzati a 1, ovvero i pin sono intesi come ingressi

digitali. Se voglio usare i pin come uscite, devo mettere a 0 i bit

corrispondenti.

Ad esempio, nel caso del bit 5, dovrò mandare a 0 il bit TRISGP2,

il che fa diventare il pin 3 una uscita digitale.

Dovendo controllare 4 I/O, i bit utilizzati sono solo i primi sei, dove c'è

la corrispondenza bit 0 a GP0 , bit 1 a GP1

e così via. Il valore assegnabile è tipico e comune per tutti i

PIC:

| 1 |

pin configurato come ingresso |

| 0 |

pin configurato come uscita |

Fa eccezione GP3:

GP3 è alternativo alla funzione di

Master Clear (MCLR), opzione scelta nella configurazione.

GP3 è alternativo alla funzione di

Master Clear (MCLR), opzione scelta nella configurazione.

Per la struttura interna del chip, il pin è utilizzabile solamente

come ingresso digitale e quindi il bit 3 di TRISGPIO è sempre fisso a

livello 1. |

Quindi, ad esempio:

- scrivendo 11111101 in TRISGPIO si

imposta come uscita il pin GP1, mentre

gli altri sono ingressi.

- scrivendo 11111000 in TRISGPIO si

impostano come uscita il pin GP0,GP1,GP2,

mentre gli altri sono ingressi.

Il registro TRISGPIO è a sola

scrittura, ovvero il suo contenuto può essere solo scritto, usando

una speciale istruzione tris,

presente nel set dei

PIC Baseline, ma non può essere riletto.

Il registro TRISGPIO è a sola

scrittura, ovvero il suo contenuto può essere solo scritto, usando

una speciale istruzione tris,

presente nel set dei

PIC Baseline, ma non può essere riletto. |

Essendo il registro in RAM, il contenuto va perso al mancare della tensione

di alimentazione; quindi si tratta di uno dei registri che è necessario

inizializzare ai valori voluti durante l'esecuzione del programma.

Però, la struttura di avvio al reset che si genera quando viene applicata l'

alimentazione (Power On Reset - POR) agisce in modo tale da

scrivere 1 in tutti i bit utili del registro. Questa pre definizione del

valore dei bit si chiama default al POR.

Quindi:

al reset, tutti gli I/O digitali sono pre configurati come

ingressi. Dovendo usarli come uscite sarà necessario mettere a 0 i

bit corrispondenti nel registro TRIS. |

|