Ulteriori informazioni tecniche

La struttura dei port

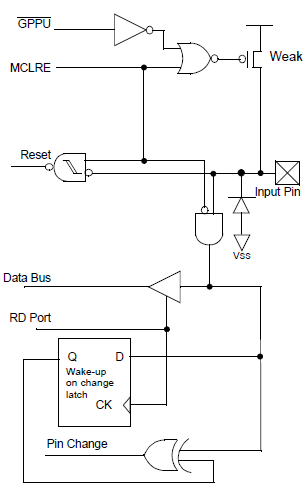

La struttura interna dei port di questi PIC è semplice.

|

I 6 I/O sono raccolti in nel port GPIO. Da un punto di vista generale GPIO

corrisponde al PORTB dei Baseline con più di 8 pin.

In lettura, il segnale RDport apre il gate che mette in comunicazione il pin

con il bus dati: la lettura riporta lo stato del pin in quel determinato

istante.

In scrittura, il segnale WRport è clock per i latch D che hanno come ingresso

quanto presente sul bus dati.

I latch del registro TRIS abilitano o meno i gate che comandano i due MOSFET

finali.

Se il bit di TRIS è a 1, i gate di MOSFET sono bloccati ed è possibile solo

la lettura, qualsiasi cosa sia scritta nel Data Latch.

Se il bit di TRIS è a 0, i gate sono comandati dallo stato dell' uscita del

Data Latch: se è a 1, viene abilitato i MOSFET P che collega il pin con la VDD;

se è 0 viene abilitato il gate del MOSFET , che collega il pin con la VSS.

|

Una coppia di diodi relazionati a VDD e VSS costituisce una protezione

contro le sovra e sotto tensioni applicate al pin. Questo è particolarmente

interessante quando si utilizza il pin come ingresso; una resistenza

esterna in serie al pin permetterà di limitare una eventuale corrente che

scorra nei diodi. Il suo valore potrà essere compreso tra 100ohm e 1k.

I due MOSFET sono simili, ma non perfettamente simmetrici; come normale, il

MOS P ha una Ron maggiore del MOS N.

La tensione di uscita a livello alto (MOSFET P attivo) è mediamente 4.5V per

VDD=5V @ 25°C con 5mA di carico.

La tensione di uscita a livello basso (MOSFET N attivo) è 0.2V per VDD= 5V

@25°C con 10 mA di carico.

Il foglio dati riporta curve relative a questi parametri in funzione della

temperatura e della corrente.

Quindi, in linea di massima, la configurazione più vantaggiosa è con il

carico appeso alla Vdd, anche se dal punto di vista pratico è la stessa cosa

una connessione sink o source current.

Per un maggiore dettaglio dei pin, occorre fare riferimento alle funzioni

ad essi collegate.

In effetti la struttura di GP0/1/2 è resa più complessa dalle

altre funzioni presenti.

- Sui pin possono essere attivati dei weak pull-up con il bit GPPU.

Questi pull-up, costruiti con MOSFET ad alta resistenza, sono

utili per evitare di aggiungere esternamente delle resistenze di

pull-up. La resistenza di questi pull-up varia tra 20 e 100k con

le caratteristiche costruttive del chip. Se la tensione di

alimentazione o la temperatura aumenta, il valore delle resistenza

è maggiore.

Questi pull-up possono essre il carico di un circuito esterno;

solamente dove le loro caratteristiche siano inadeguate all'

applicazione si utilizzeranno pull-up esterni.

- Sui pin è programmabile la funzione di reset alla variazione di

stato, creata con un latch addizionale e un gate EXOR. Se la

funzione è abilitata, il gate verifica l'ultimo valore letto,

conservato nel latch, con quello attuale del pin: se esiste una

differenza, agisce sul circuito generatore del reset interno.

Anche per il pin GP2 sono implementate variazioni dello schema base allo

scopo di supportare le funzioni addizionali

La logica interna del pin GP2 comprende uno switch dipendente dal registro OPTION consente al pin di

diventare ingresso esterno T0CKI per il Timer0. In questo caso il

segnale diretto al timer è condizionato da un gate Schmitt Trigger. Se l' opzione è scelta, il pin non può

assumere altre funzioni.

Non è previsto il weak pull-up, ne la funzione di wakeup.

|

Il pin GP3 :

- ha la funzione di weak pull-up programmabile come GP0 e GP1

- ha la funzione di wake up per cambio dello stato sul pin

- è impostabile dalla Configuration Word come MCLR o ingresso

digitale.

Come I/O digitale, ha solo il registro di ingresso e non può

essere usato come uscita

E' evidente che la scelta tra MCLR e GP3, essendo parte del

registro di configurazione, è fissa fino a nuova

programmazione.

La funzione di ingresso diventa attiva automaticamente quando MCLR è

disabilitato.

- dispone di un particolare meccanismo che, all' applicazione

della tensione Vpp (10-13V) avvia le operazioni di accesso alla

lettura, scrittura e verifica della memoria programma attraverso

l' interfaccia ICSP. In queste condizioni, GP0 e GP1 passano ad

essere le due line di comunicazione sincrona.

|

I pin GP4 e GP5 supportano l' oscillatore esterno:

La scelta tra I/O digitale e oscillatore è effettuata nella Configuration

Word. A causa della loro struttura non dispongono di Weak pull-up e della

funzione di wakeup.

La tabella seguente riassume la situazione dei pull up e della funzione di

wakeup.

| Pin |

WeakPU |

WakeUp |

| GP0 |

s |

s |

| GP1 |

s |

s |

| GP2 |

- |

- |

| GP3 |

s |

s |

| GP4 |

- |

- |

| GP5 |

- |

- |

| GP6 |

- |

- |

Se MCLR è abilitato nella Configuration Word, il weak pull-up relativo è

attivato automaticamente (ma non è attivato il wakeup). Questo permette di

fare a meno di una resistenza esterna.

Il tipo di ingresso o di uscita che viene implementato sui pin a seconda

della funzione è questo:

| Pin |

Funzione |

Ingresso |

Uscita |

Note |

| 7 |

GP0

|

TTL

|

CMOS

|

I/O digitale bi direzionale con weake pull-up e wake-up programmabili

|

|

ICSPDAT

|

ST

|

CMOS

|

ICSP dati - ingresso con Schmitt Trigger,

uscita CMOS

|

| 6 |

GP1

|

TTL

|

CMOS

|

I/O digitale bi direzionale con weake pull-up e wake-up programmabili

|

|

ICSPCLK

|

ST

|

CMOS

|

ICSP clock - ingresso con Schmitt Trigger, uscita CMOS

|

| 5 |

GP2

|

TTL

|

CMOS

|

I/O digitale bi direzionale con wake pull-up e wake-up programmabili

|

|

T0CKI

|

ST

|

-

|

Clock Timer0, ingresso con Schmitt

Trigger

|

| 4 |

GP3

|

TTL

|

-

|

Ingresso digitale con weake

pull-up e wake-up programmabili

|

|

MCLR

|

ST

|

-

|

Ingresso MCLR con Schmitt Trigger

|

|

Vpp

|

HV

|

-

|

Ingresso tensione di programmazione

|

| 3 |

GP4

|

TTL

|

-

|

I/O digitale bi direzionale con wake pull-up e wake-up programmabili

|

|

OSC2

|

-

|

XTAL

|

oscillatore esterno - uscita

|

| 2 |

GP5

|

TTL

|

-

|

I/O digitale bi direzionale con wake pull-up e wake-up programmabili

|

|

OSC1

|

ST

|

|

oscillatore esterno - ingresso

|

- TTL = ingresso livelli TTL

- CMOS = uscita livelli CMOS

- ST = ingresso Schmitt trigger

- HV = ingresso per la tensione di programmazione

- XTAL = uscita per l''oscillatore a quarzo esterno

I pin hanno diversa configurazione in ingresso a seconda della

funzione attivata. Ad esempio, il pin 5 è un ingresso TTL quando è GP2 e un

ingresso Schmitt Trigger quando serve da ingresso del conteggio del timer.

Tutti i pin sono protetti da una coppia di diodi tra Vdd e Vss, escluso GP3

che ha solo il diodo verso la Vss (l' altro è assente a causa della

necessità di applicare la Vpp che è maggiore della Vdd).

Altri parametri

I chip possono lavorare a piena frequenza (4 e 8MHz) tra 2.2 e 5.5V per

temperature ambiente tra -40°C e +125°C (per i chip con gamma di temperatura

estesa).

Per quanto riguarda l' oscillatore esterno, i limiti indicati sono questi:

| Oscillatore |

Frequenza massima |

| LP |

100kHz |

| XT |

4MHz |

| EXTRC |

4MHz |

| INTOSC |

4-8MHz |

WDT ha un minimo di 10ms circa (@-40°C e VDD=5.5V) che sale a 45 ms

(@+125°C e 2.2V).

Il foglio dati riporta grafici relativi a questo parametro.

Il tempo DRT dipende dall' oscillatore selezionato e dal tipo di reset:

| Oscillatore |

POR |

Altri |

| INTOSC e EXTRC |

1ms (0.5-2ms) |

10 us |

| LP e XT |

18ms (9-40ms) |

La massima corrente al pin Vss è 200 mA e 150 mA al pin Vdd; in entrambi i

casi è garantita la corrente di 25mA a tutti i pin.

|