Indirizzi speciali

Per quanto riguarda gli indirizzi, lo standard ne prevede alcuni collegati a funzioni

speciali:

| Indirizzo |

R/W |

Note |

| 0000 000 |

0 |

indirizzo della General Call |

| 0000 000 |

1 |

Start bit. Nessun dispositivo risponde a questo indirizzo con un ACK |

| 0000 001 |

x |

Indirizzo riservato per mescolare dispositivi CBUS e I2C

sullo steso bus.

I dispositivi I2C non rispondono a questo indirizzo. |

| 0000 010 |

x |

Riservato per la compatibilità di altri dispositivi con il bus I2C. |

| 0000 011 |

x |

Riservato per future applicazioni |

| 0000 1xx |

x |

Riservato al master in modo high speed |

| 1111 1xx |

x |

Riservato per future applicazioni (identificazione ID) |

| 1111 0xx |

x |

indirizzo a 10 bit |

Vediamo qualche dettaglio.

General Call

L'indirizzo di General Call (chiamata generale) viene utilizzato per

trasmettere a tutte le periferiche dell'intero bus, indipendentemente dalla loro indirizzo.

Va tenuto conto, però, che non tutti i dispositivi supportano questa funzione

e ignoreranno la chiamata.

Se il dispositivo non supporta la General Call o non richiede

dati dopo questa, non risponde con un acknowledgement. Se, invece, lo Slave

richiede dati dopo la chiamata, genera un ACK.

Il significato della General Call è precisato dal secondo byte

che segue l' indirizzo di chiamata; in particolare il bit 0 ha una

funzione di definizione particolare.

Se il bit 0 del byte dati è uguale a 0, il byte dati ha le seguenti

possibilità:

- 00000110 (06h) - reset software e scrittura della parte

programmabile dell' indirizzo dello Slave. Il dispositivo che accetta

questo byte resetta il suo hardware interno; inoltre tutti i dispositivi

che definiscono la parte programmabile del loro indirizzo in hardware

ricaricano questa parte programmabile. Il dispositivo però non resetta.

- 00000100 (04h) - scrittura della parte programmabile dell'

indirizzo dello Slave. Tutti i dispositivi che definiscono la parte

programmabile del loro indirizzo in hardware ricaricano questa parte

programmabile. Il dispositivo però non resetta.

- 00000000 (00h) - Codice riservato

Se il bit 0 è uguale a 1, significa che questa chiamata è

effettuata da un dispositivo Master hardware che non dispone di alcuna informazione preliminare degli indirizzi slave collegati. In questo caso il master fa la chiamata con il proprio indirizzo in modo che gli

slave possono identificare la fonte del messaggio: i sette bit più

significativi del secondo byte contengono l' indirizzo di questo Master.

Questo permette ad un dispositivo intelligente, come un microcontroller, di

rilevare la presenza del master hardware; se questo può operare anche come

Slave, il suo indirizzo Slave sarà quello trasmesso.

La gestione della General Call ha anche lo scopo di realizzare sistemi auto

configuranti, implementando sul Master configuratore gli opportuni algoritmi.

START bit

Un microcontroller può essere collegato al bus I2C in due modi:

- se dispone di una un'interfaccia on-chip hardware per la gestione del bus I2C può essere programmato per essere interrotto

dalle condizioni di Start sul bus.

- se il dispositivo non dispone di un'interfaccia, deve monitorare costantemente

il bus via software.

Ovviamente, più volte il microcontroller effettua sondaggi sul bus (polling),

meno tempo ha a disposizione per eseguire altre funzioni. C'è quindi una differenza di velocità tra dispositivi

con un supporto hardware e quelli senza che si basano su polling software. In questo caso, il trasferimento dei dati può essere preceduto da una procedura di

Start che è molto più lunga del normale. La procedura di partenza è costituito da:

- un invio della condizione di Start

- l' invio del byte di start (0000 0001)

- un acknowledge del clock (ACK)

- una condizione di Restart (Sr).

Dopo la condizione di Start che è stata trasmessa da un master per

accedere al bus, viene trasmesso il byte riservato START (0000 0001). Un altro

microcontroller può quindi testare la linea SDA con una frequenza di

campionamento relativamente bassa fino a quando uno degli zeri nel byte START viene rilevato. Dopo il riscontro di questo livello basso sulla linea SDA, il

microcontroller può aumentare la frequenza di campionamento per identificare la condizione di

Restart che viene poi utilizzata per la sincronizzazione. Un ricevitore hardware verrà

reimpostato al ricevimento della condizione di Restart e quindi ignorerà il byte di inizio. Un acknowledge

viene generato dopo il byte di inizio solo per conformarsi con formato utilizzato sul

bus, dato che a nessun dispositivo è consentito di rispondere con un ACK al

byte di Start.

Attraverso il byte di Start è possibile implementare anche sistemi di auto

rilevamento degli elementi sul bus e auto configurazione del sistema.

CBUS

Ricevitori CBUS possono essere collegati al bus I2C . Tuttavia,

CBUS utilizza un terzo conduttore, detto DLEN, che assume

funzione di acknowledge e sostituisce la condizione ACK del bus I2C.

Anche il formato dei dati può essere differente: normalmente, in I2C

le trasmissioni sono sequenze di byte di 8 bit, mentre i dispositivi compatibili CBUS hanno diversi formati.

Ne risulta che, per poter realizzare una struttura mista in cui sul bus I2C

si trovano anche dispositivi CBUS, si utilizza uno speciale indirizzo (0000001X)

a cui essi rispondono.

Dopo la trasmissione dell'indirizzo CBUS, la linea DLEN può essere attivata e

inviata una trasmissione in formato CBUS. La trasmissione è chiusa da una condizione STOP, riconosciuta da tutti i dispositivi.

Compatibilità con altri dispositivi

I2C prevede la possibilità di inserire sullo stesso bus

dispositivi che usino lo stesso hardware, ma differente protocollo. All'

indirizzo 0000010X risponderanno i dispositivi che appartengono a questa

categoria e i dispositivi I2C che rispondono ad entrambi i

protocolli.

High speed

I2C prevede una estensione con clock fino a 3.4MHZ, chiamata high speed (Hs).

I dispositivi ad alta velocità sono compatibili verso il basso, permettendo per sistemi bus misti.

I segnali in modo HS sono identificati come SDAH e SCLH e sono applicate varie

modifiche allo standard finora descritto.

Per abbreviare il tempo di salita del segnale a 3.4 MHz, i Master dispositivi hanno una combinazione di un open-drain pull-down e

un generatore di corrente pull-up su SCL, abilitato durante il modo Hs e solo per un

Master. I Master Hs generano un segnale di clock seriale con rapporto tra il

periodo basso e quello alto di 1: 2.

Le periferiche possono avere un ponte incorporato per separare il dispositivo a bassa velocità

dal bus durante il trasferimento ad alta velocità: lo scopo principale di tale ponte è di ridurre il carico capacitivo sul bus ed evitare

possibili conflitti causati da dispositivi a bassa velocità.

Lo schema di indirizzamento per i trasferimenti ad alta velocità si differenzia dalla normale procedura di indirizzamento.

Una trasmissione ad alta velocità si avvia in modalità full o standard, cioè al

massimo 400 kbit.

- Dopo la condizione di Start viene trasmesso un byte '00001XXX', seguito

da un not-acknowledge obbligatorio. I tre bit meno significativi vengono utilizzati per identificare

diversi Master sullo stesso bus, ognuno dotato del suo identificatore univoco. Durante la trasmissione del codice

si può avere una situazione di arbitraggio, così che solo un Master

acquisti il controllo del bus. L' arbitraggio, però, non avviene in Hs.

Con gli ultimi 3 bit dell' indirizzo speciale possono far parte del bus ad

alta velocità fino a 8 Master, anche se il codice '00001000' dovrebbe essere riservato per scopi diagnostici e

test.

- Dopo la fase di acknowledge, il trasferimento ad alta velocità inizia con una condizione di avvio ripetute, seguita dall'indirizzo

Slave e da i dati successivi, come in modalità Fast o Standard, ma con un

clock che può arrivare a 3.4 MHz.

- Il generatore di corrente, attivato dopo la trasmissione del codice

iniziale, viene disattivato dopo ogni Restart o ACK o NACK per dare modo

allo Slave di operare il clock stretching

- La modalità ad alta velocità rimane attiva fino a quando viene

trasmessa una condizione di Stop, sulla quale i dispositivi collegati ad alta velocità tornano a rallentare la trasmissione come modalità Fast o

Standard

Nell'immagine qui sotto viene esemplificato l'inizio di un trasferimento ad alta velocità.

Bus con questa velocità di clock richiedono dispositivi

particolari e una struttura hardware molto curata e non sono comuni.

Maggiori informazioni su questa modalità sono descritti nella documentazione

linkata alla fine di questo tutorial.

Indirizzo a 10 bit

Il sistema degli indirizzi si rende necessario proprio per la natura del

bus; abbiamo visto che lo shift register tipico di I2C ha una capacità di 8 bit

e questo limita la dimensione di un indirizzo a soli 7 bit.

E l' invio di un pacchetto di 7 bit rende possibile l' accesso a 128 dispositivi.

Si tratta comunque di quantità teorica, dato che nella realtà esistono due limiti: l' estensione fisica e

le caratteristiche elettriche del bus e, come abbiamo visto, il fatto che vari indirizzi sono

utilizzati per funzioni speciali.

Lo standard, però, ha previsto la possibilità di estendere il numero delle

periferiche indirizzabili a 1024 utilizzando indirizzi a 10 bit.

E' evidente che, disponendo solo di pacchetti a 8 bit, occorrano due emissioni

successive per completare l' indirizzo a 10 bit.

Per distinguere questa sequenza di due byte di indirizzo da una qualsiasi

altra trasmissione di dati, il primo byte di indirizzo dovrà essere 1111 0xx.

I due bit meno significativi costituiscono i due bit più alti dell' indirizzo

a 10 bit; il successivo byte completerà questo indirizzo. L' ottavo bit del

primo byte è sempre riservato all' indicazione R/W.

Dispositivi con indirizzi 7 e 10 bit possono essere collegati allo stesso bus.

Ne consegue che non ci potranno essere dispositivi con indirizzo a 7 bit nell'

area 1111000-1111011 (78h-7Bh).

Attualmente, l' indirizzamento a 10-bit non viene ampiamente utilizzato,

ma, in generale, i moduli di comunicazione sincrona dei microcontroller

prevedono anche questa opzione.

Tutte le combinazioni di formati di lettura/scrittura sono possibili si con indirizzamento a

7 che a 10 bit. Vediamone due:

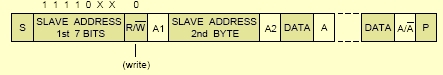

- Il Master-trasmettitore trasmette al ricevitore Slave con un indirizzo

a 10 bit. La direzione di trasferimento è unica. Quando un indirizzo

10 bit segue una condizione di Start, ogni periferica confronta i primi sette bit del primo byte dell'indirizzo

(1111 0XX) con il proprio indirizzo e verifica se l'ottavo bit (R/W) è 0. È possibile che più di un dispositivo

trovi questa coincidenza e generi un acknowledge (A1). Ora i

dispositivi confronteranno gli otto bit del secondo byte dell'indirizzo

con i propri indirizzi, ma solo uno potrà trovare una corrispondenza e generare

il secondo acknowledge (A2). Lo Slave corrispondente rimarrà in

comunicazione con il Master fino a che riceve una condizione di STOP (P) o una condizione

RESTART (Sr), seguita da un indirizzo diverso.

|

|

|

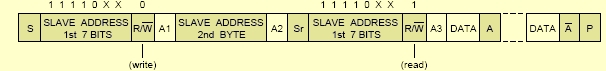

- Il Master-ricevitore legge dati da uno Slave-trasmettitore con un indirizzo

a 10 bit. La direzione di trasferimento è cambiata dopo il secondo bit

R/W. La procedura è la stessa di quella descritta prima. Dopo il

Restart (Sr), una periferica corrispondente all' indirizzo si ricorda che esso è

stato inviato prima, quindi controlla se i primi sette bit del primo byte

dell' indirizzo seguito a Sr sono gli stessi, come se si trattasse

di un indirizzo dopo la condizione di Start (S) e verifica se l'ottavo bit (R/W) è 1. Se esiste una corrispondenza, lo

Slave genera riconoscere un ACK (A3). Il trasmettitore Slave rimane

in connessione fino a quando riceve una condizione di STOP (P) o fino a quando non riceve un altro

Restart (Sr) seguito da un indirizzo diverso. Dopo il Restart, tutti gli altri dispositivi

confrontano i primi sette bit del primo byte dell'indirizzo (1111 0XX) con i propri indirizzi e

testano l'ottavo bit (R/W). Tuttavia, nessuno di loro entrerà in

linea perché R/W = 1 (per periferiche a 10-bit) o per l'indirizzo

0XX 1111 (per le periferiche di 7 bit) non corrisponde.

|

|

|

Il fatto che più periferiche mandino a livello basso la line SDA al

momento della generazione del primo ACK (A1) non crea alcun problema al bus:

ricordiamo che si tratta di un open collector-open drain e quindi qualunque

dispositivo può mandare a livello basso la linea. Con la linea a livello

basso sul nono colpo di clock, il Master rileverà un ACK e procederà con l'

invio del secondo elemento dell' indirizzo, alla cui verifica risponderà

questa volta una sola periferica (in quanto è obbligo che non esistano sul

bus due elementi con lo stesso indirizzo completo).

In un bus misto di periferiche a 7 e 10 bit, quelle a 7 bit non entreranno mai

in comunicazione quando un Master invia un indirizzo a 10 bit dato che il

primo byte non corrisponde ad alcuno dei loro possibili indirizzi. Per contro,

nessuna periferica a 10 bit potrà rispondere ad una chiamata con indirizzo a

7 bit, dato che per attivarsi deve ricevere il primo byte di indirizzo

speciale.

Uno dispositivo con indirizzo a 10 bit, però, se abilitato, reagirà a una

chiamata generale nello stesso modo dei dispositivi a 7 bit, in quanto per

attivare questa funzione bastano i sette bit dell' indirizzo di General Call.

Master hardware sono in grado di trasmettere il loro indirizzo a 10 bit dopo

la General Call, con l' invio di due bytes, dove il primo byte di dati contiene

gli otto bit meno significativi dell'indirizzo.

ID

I dispositivi I2C contengono opzionalmente 3 bytes (24 bit) di

identificazione del componente:

- 12 bit costituiscono l' identificatore del costruttore

- 9 bit definiscono l' identificatore del componente

- 3 bit definiscono la revisione assegnata dal costruttore

Con l' indirizzo riservato 11111000 è possibile accedere alla lettura di

questo identificatore.

La funzione è descritta nella documentazione del bus di NXP.

L' identificatore del costruttore viene assegnato dal comitato di gestione

del bus I2C.

|