Funzioni particolari

La manipolazione delle linee SDA e SCL consente di introdurre alcune

condizioni speciali che aumentano la flessibilità e l' efficienza del bus.

Sono:

- clock stretching

- clock synchronization

- arbitraggio

CLOCK STRETCHING

Una delle caratteristiche più significative del protocollo è il clock

stretching (letteralmente "allungamento del clock"). Questa azione

ha lo scopo di dare ai dispositivi "lenti" abbastanza tempo per

rispondere.

Se un dispositivo è lento, è possibile che occorra un certo tempo prima

di aver elaborato il dato ricevuto; in questo caso la periferica Slave è

autorizzata a portare a livello basso la linea SCL e a mantenerla a questo

livello fino a che è necessario, indicando che non è ancora pronta per elaborare i

altri dati.

Da parte sua il Master, rilasciando la linea del clock, dovrà

verificare che essa ritorni effettivamente a livello alto per via dei

pull-up; se questo non succede è indice che lo Slave sta chiedendo più

tempo. Ne deriva che il Master arresta le operazioni fino a che SCL non viene

rilasciata (questo è possibile perchè, ricordiamo, le linee del bus sono

open drain - open collector e vanno a livello alto attraverso i pull-up).

Anche se il Master può tenere la linea SCL a livello basso come desidera, il termine

"clock stretching" è normalmente utilizzato solo quando l' azione

è eseguita da uno Slave.

Il clock stretching è l' unico momento in cui uno Slave può manipolare la

linea SCL.

Se su un bus nessun dispositivo può richiedere il clock stretching,

il Master non ha necessità di controllare questa funzione.

A livello di bit, in teoria qualsiasi impulso di clock può essere

allungato, come nel caso in cui il clock del Master sia troppo rapido per lo

Slave. A livello di byte, un dispositivo può essere in grado di ricevere

un dato, ma richiedere tempo per elaborarlo e quindi operare un clock stretching

dopo l' ACK con lo scopo di arrestare la trasmissione del Master per il tempo

necessario. In modo High Speed il clock stretching è ammesso solo a livello

di byte.

Alcuni dispositivi non hanno la possibilità di supportare il clock

stretching e potranno essere indicati come "2-wires interface" e non

come I²C puri.

Da notare che, per garantire un transfer rate minimo, SMBus pone dei limiti

alla lunghezza del clock e i dispositivi non possono bloccare il bus oltre un

certo tempo.

Clock synchronization

Due Master possono iniziare a trasmettere contemporaneamente sul bus inattivo.

E' evidente che questa circostanza è inaccettabile, in quanto la trasmissione

dei dati sarebbe corrotta dall' accesso contemporaneo di due unità che

cercano di inviare bit differenti. Occorre, quindi, un sistema di arbitraggio per decidere

quale unità prenderà il controllo del bus e completerà la sua trasmissione.

Questa operazione è svolta dal clock synchronization e dall'arbitraggio.

Ovviamente se sul bus è presente un solo Master, queste funzioni non sono

necessarie.

La sincronizzazione del clock si basa sulla linea SCL che è un wired-AND

di open collector-open drain.

Tutti i Master generano il proprio clock e i dati sono validi durante il

periodo di livello alto del clock.

E' possibile che i clock di diversi Master siano differenti ed è necessario

per l' arbitraggio, che procede bit per bit, che i clock siano uguali.

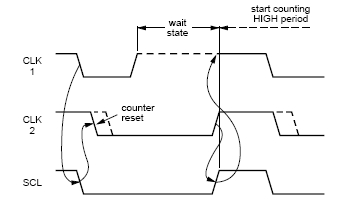

Il diagramma rende graficamente la situazione.

|

La transizione da livello alto a livello basso della linea SCL causerà

da parte dei Master un conteggio basato sul proprio periodo di clock.

Se il Master rilascia SCL, ma la linea non ritorna a livello alto,

questo significa che un altro Master la sta impegnando. Non si può cambiare lo stato della linea di SCL se un altro

clock la sta tenendo a livello basso; quindi SCL resterà a livello

basso per il periodo del clock più lento, mentre il Master con il

periodo più breve porterà il suo switch della linea SCL ad alta

impedenza e aspetterà in wait state. |

Quando tutti i master interessati hanno esaurito il loro conteggio del periodo

a livello basso, la linea di clock sarà rilasciata e andrà a livello alto. Non ci sarà quindi alcuna differenza tra

i clock dei Master e lo stato della linea SCL; tutti i Master inizieranno a contare i loro periodi

di livello alto nello stesso momento. Il primo Master che completa il suo periodo,

costringerà nuovamente la linea SCL basso. In questo modo viene generato un

clock SCL sincronizzato nel periodo a livello basso, determinato dal Master con il più lungo periodo di

livello basso e il periodo a livello alto determinato da quello con il più breve periodo

a livello alto.

Arbitraggio

L' arbitraggio, come la sincronizzazione del clock, si riferisce ad una porzione del protocollo richiesto solo se verrà

utilizzato più di un Master nel sistema. Gli Slave non sono coinvolti in

queste procedure.

Un Master può iniziare un trasferimento solo se il bus è libero, ovvero

entrambe le linee a livello alto, sostenute dai pull-up. Il Master che rileva il bus libero

genererà una condizione di Start entro il tempo minimo di attesa

stabilito dalle specifiche (tHD; STA); però è possibile che due Master

cerchino di accedere al bus nello stesso momento: l'arbitraggio è quindi

necessario per determinare quale Master prenderà il controllo. L'

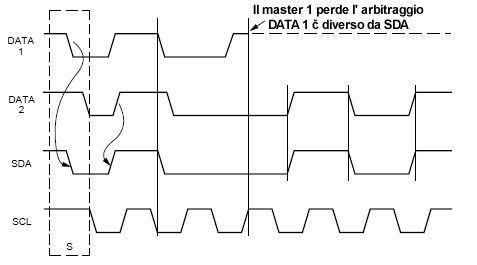

arbitraggio procede bit per bit: durante ogni bit, mentre SCL è a livello alto, ogni

Master controlla il livello di SDA per vedere se corrisponde a quello che ha inviato. Questo processo potrebbe richiedere

un certo numero di bit: i Master sono effettivamente in grado di completare un'intera transazione senza errore, fintanto che il

dato trasmesso è identico, ma se il Master 1 tenta di inviare un

livello alto mentre l' altro invia un livello basso, sa che ha perso l'arbitrato e

disconnette il driver di uscita SDA, mentre il Master 2 va a completare la transazione. Nessuna informazione viene persa durante il processo di

arbitraggio.

|

Un Master che perde l'arbitraggio può generare impulsi di clock fino alla fine del byte in cui perde

l'arbitraggio e dovrà riavviare la transazione quando il bus sarà

libero.

Se un Master incorpora anche una funzione di Slave e perde l' arbitraggio durante la fase di

indirizzamento, è possibile che il Master vincente stia cercando di

indirizzarlo; il Master perdente deve quindi passare immediatamente alla sua modalità di

Slave |

Siccome il controllo del bus è deciso esclusivamente sull'indirizzo e i dati inviati dai

Master concorrenti, il protocollo non prevede alcun Master a livello superiore, né alcun ordine di priorità sul bus.

Di conseguenza si potrebbero verificare condizioni non definite nelle seguenti

situazioni:

- Un Master invia una condizione di Restart mentre un'altro sta inviando bit di dati.

- Un Master invia una condizione di STOP e l' altro sta inviando dati.

- Un Master invia una condizione di Restart e l' altro invia uno Stop

Auto incremento

Dispositivi I2C dotati di un'area dati di dimensioni consistenti, come RAM

o EEPROM o Flash, implementano un automatismo per cui il dispositivo mantiene

un puntatore interno che viene incrementato automaticamente su dati da leggere o scrivere;

questa funzione che può essere impostato manualmente oppure interamente

automatica. Questo è utile per acedere ad una succesione di dati in modo

ordinato ed efficiente.

L' incremento automatico non è parte dello standard I2C, ma è una caratteristica comune in molti dispositivi I2C.

Una tipica sessione di comunicazione è questa:

- Il Master invia una condizione di Start

- Segue un byte dell'indirizzo dello Slave con il bit di lettura/scrittura

in modo da impostare il il puntatore dell'auto incremento

- Se la funzione è supportata, il Master invia il dato di auto incremento

- Il Master invia una condizione di Restart per leggere dati a partire da posizione

iniziale dell' area puntata

- Il Master invia un byte dell'indirizzo a cui accedere

- e legge/scrive un numero arbitrario di byte dal dispositivo: la caratteristica

auto incremento fa si che il puntatore interno, ad ogni accesso, sia

modificato, permettendo di accedere a byte consecutivi senza ulteriori

invii di indirizzo

- Terminato il trasferimento, il Master rilascia il bus con una condizione

di Stop

Ovviamente sarà necessario consultare i fogli dati dei singoli dispositivi

per verificare la possibilità di auto incremento e i le relative operazioni

necessarie.

Rilevamento degli elementi sul bus e auto

configurazione

Utilizzando, ad esempio, il byte di Start è possibile implementare

sistemi di identificazione delle periferiche sul bus e modalità di auto

configurazione del sistema molto complessi. La sequenza tipica è

- < Indirizzo primario > + W

- <byte di Start 00000001>

- < Indirizzo secondario >

- < DeviceType> < Sensor String > < Indirizzo Sensore >

Sono classificabili i DeviceType, che contiene la descrizione della classe

di appartenenza del dispositivo (ad esempio Sensori, battery manager,

dispositivi di comunicazione, GPS, terminatori, ecc) e i SensorString, che

contengono le specifiche del sensore (temperatura, pressione, velocità,

umidità, ecc) in modo da permettere al un Master di configurazione di operare

una configurazione dinamica del bus

|