L' hardware del bus

Va osservato che la Vdd del bus non è specificata come valore, ma solo

attraverso i parametri

- livello alto VIH = 0.7 Vdd e

- livello baso VIL = 0.3 Vdd,

per cui, se normalmente il bus utilizza la Vdd di alimentazione dei

componenti digitali (da 2.5 a 5 V), nulla vieta che essa sia maggiore, ad

esempio 15 V.

Il limite della tensione Vdd dipenderà dalle caratteristiche dei dispositivi

e dalla corrente che possono commutare. La specifica indica i limiti 3 mA per

il modo standard e 20 mA per il modo Fast, ma molti dispositivi possono

trattare anche correnti maggiori.

La corrente sarà limitata dal valore dei pull-up:

Rp (min) = [Vdd - VOL(max)

] / IOL

La necessità dei

pull-up rende pure necessario adeguarne il valore alla capacità della linea,

abbassandone il valore con l' aumentare della frequenza di comunicazione. I

valori tipici vanno da 2 k per clock a 400 kHz, fino a 10 k per clock

inferiori a 100 kHz. Microchip, nel documento Getting Started:I2C Master Mode

consiglia:

| <100 kHz |

100 kHz |

400 kHz |

| 4k7 |

2k2 |

1k |

Va notato che, con il ridursi

del valore dei pull-up, aumenta la corrente quando i dispositivi comunicano,

il che rende il bus I2C non ideale per applicazioni a basso

consumo.

In ogni caso, la documentazione di NXP fornisce indicazioni per il calcolo

del valore dei pull-up.

Considerando che il livello alto è definito come VIH = 0.7 Vdd

e il livello baso come VIL = 0.3 Vdd, occorre conoscere il

valore della capacità Cb della connessione per determinare

il valore della costante RC di capacità e resistenza del pull-up Rp.

Il valore dei pull-up sarà dato da:

Rp (max) = tr / 0.8473 Cb

dove tr è il tempo minimo di salita della

commutazione, dipendente dal clock e rilevabile dalle tabelle fornite dal

costruttore. Come ordine di grandezza, ecco dei valori approssimati in

dipendenza dalla frequenza del clock:

in funzione della capacità

Cp

[pF] |

Rp [kohm] |

| standard |

fast |

fast plus |

| 100 |

12 |

4 |

1.5 |

| 200 |

6 |

2 |

0.5 |

| 300 |

4 |

1 |

0.5 |

| 400 |

3 |

1 |

0.5 |

|

|

in funzione della tensione

Vdd

[V] |

Rp [kohm] |

standard

e fast |

fast plus |

| 2.5 |

0.5 |

0.2 |

| 5 |

1.5 |

0.3 |

| 10 |

2.7 |

0.4 |

| 15 |

3.5 |

0.5 |

|

I valori sopra riportati sono puramente indicativi, tratti dai diagrammi

forniti nella documentazione di NXP.

Se la frequenza e/o la capacità di linea aumentano, il bus richiederà dei

pull-up attivi, ovvero dei generatori di corrente, in modo da avere una

compensazione del carico capacitivo e quindi una buona qualità dei fronti di

commutazione.

Ci sono vari metodi base per implementare questo:

- uno specchio di corrente (current mirror)

- una resistenza ed un diodo di calmping a partire da una tensione più

elevata

- una generatore di corrente costante a FET o un diodo a corrente costante

bipolare

- un integrato specifico, ad esempio LTC4311 di Linear Technology

Qui sotto, come esempio, l' applicazione di LT4311, presa dal foglio dati

del componente, e, a lato, la forma d' onda della commutazione sulla linea in

cui si nota chiaramente l' effetto positivo del generatore di corrente

rispetto al solo pull-up.

Per quanto riguarda i collegamenti del bus, occorre essenzialmente che le

capacità parassite sia contenute entro un valore tale da non creare problemi

ai fronti di commutazione. Anche se il nome dello standard fa riferimento a

connessioni tra circuiti integrati, quindi all' interno dello stesso circuito

stampato, sono stati realizzati buffer per trasportare la connessione I2C

a molti metri di distanza, come il repeater P82B96 che consentirebbe di

arrivare a 1000 m, ma con la riduzione del clock ad una trentina di kHz. Tipicamente il limite

di capacità della connessione è 400 pF, il che consente di

superare vari metri utilizzando cavi che non abbiano capacità superiore a

40-50 pF/m (Belden, cavi STP, ecc). Però, come è evidente, la frequenza massima a

cui la trasmissione è possibile sarà in funzione non solo delle

caratteristiche dei dispositivi collegati, ma anche di quelle del collegamento

e,

come per ogni altro caso di bus remotati, la trasmissione è

possibile con sicurezza in relazione alla frequenza di trasmissione, alle

caratteristiche dei cavi, al rumore indotto dall' ambiente e, dato che si

tratta di una connessione sigle-ended, ai ground bounces.. Ne deriva che, pur

essendo possibile remotare elementi di un bus I2C anche a distanze

considerevoli, sarà più sensato dare la preferenza ad altri tipi di

interfaccia previsti proprio per questa situazione (CAN, RS-422/485, Ethernet,

ecc).

All' atto pratico, al di fuori del circuito stampato, è consigliabile usare:

- flat cables fino a qualche decina di centimetri

- cavi piatti twistati (dati+gnd e clock+gnd) per distanze dell' ordine

del metro

- cavi schermati e twistati per lunghezze maggiori

mantenendo le alimentazioni separate e ben disaccoppiate ad ogni

periferica. Peraltro lo standard non specifica particolari cavi o connettori,

per cui ogni costruttore è ragionevolmente libero nella scelta dei componenti

da utilizzare. La stessa documentazione di Philips, però, consiglia di usare

connessioni a 4 fili intrecciati; i conduttori dei segnali (clock e dati) non

vanno intrecciati tra di loro per limitare la mutua induzione, o crosstalk,

ma preferenzialmente sono associati ad un cavo di massa (gnd) con lo scopo di

mantenere costante l' impedenza e di minimizzare il crosstalk.

Nel caso in cui le capacità parassite siano superiori al limite di 400 pF,

si potrà suddividere il bus in sezioni attraverso un buffer o dei multiplexer.

Come nel caso esemplificato ( o in quello più complesso presentato all'

inizio del tutorial). Tra l' altro, una simile configurazione permette l'

impiego di due Vdd differenti.

Sempre nel caso di Vdd differenti, sono disponibili traslatori di livello per

adeguare le periferiche sullo steso bus.

NXP ha realizzato numerosi dispositivi per il supporto hardware al bus e

sono virtualmente coperte tutte le possibili applicazioni. Le application

notes di NXP AN255, I2C / SMBus Repeaters, Hubs and Expanders e AN262,

PCA954x Family of I2C / SMBus Multiplexers and Switches illustrano

queste possibilità.

|

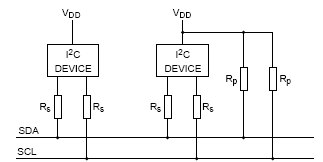

Una ulteriore nota è utile dare riguardo alla possibilità di

proteggere i dispositivi sul bus da possibili sovratensioni, inserendo

in serie delle resistenze.

L' aggiunta delle resistenze Rs richiede un ricalcolo dei pull-up.

La documentazione di NXP fornisce informazioni anche relativamente

a questo aspetto. |

Come ordine di grandezza per le resistenze serie:

| Rp |

Rs (ohm) |

| Vdd = 2.5V |

Vdd = 5 V |

| 10 k |

500 |

1k5 |

| 4 k |

200 |

600 |

| 2 k |

100 |

300 |

| 1 k |

75 |

100 |

Esistono comunque dispositivi che integrano già sistemi di protezione

contro sovratensioni.

|

In applicazioni critiche è indispensabile aggiungere un sistema di

isolamento completo tra unità a microcontroller e periferiche remote:

questo evita i potenzialmente dannosi loop di terra, i rischi per l'

operatore e i disturbi raccolti dalle linee.

Un esempio è rappresentato da un componente specifico di Analog

Devices.

|

Si tratta di isolatore galvanico ADUM1250, hot swappable a due canali

(due bus I2C oppure PBUS o SMBUS). Può operare fino a 1 MHz e con un

isolamento di 2.5 kV.

Altri produttori di dispositivi analoghi sono Silicon

Labs o Linear

technology.

Un efficace isolamento può essere effettuato anche con opto isolatori.

I moduli di comunicazione sincrona

Un drive per shift register può essere scritto con semplicità per

qualsiasi microcontroller, ma clock elevati e trasmissioni complesse come

quella di I2C costituiscono situazioni gravose da emulare in software.

In particolare risulta molto impegnativo realizzare gestioni che non siano in

polling e del genere bit-banging.

Per evitare questo carico all' utente, nei principali microcontroller viene

integrata una periferica specifica per la comunicazione sincrona, dotata di

meccanismi di buffer e di flag per la gestione sia in polling che in interrupt.

In genere questi moduli sono in grado di gestire diversi formati, ad esempio

SPI, I2C e SMBus.

Nel modulo di gestione

seriale sincrona tipico di un microcontroller, per i PIC chiamato MSSP o SSP

(Master Synchronous Serial Peripheral o Synchronous Serial

Peripheral), sono presenti, oltre agli shift

register (SSPSR nell' immagine sotto), anche dei buffer (SSPBUF nell' immagine) per conservare il dato ricevuto.

Possiamo notare la complessità che non si limita ad un solo

registro di spostamento, ma ha come elemento essenziale una complessa logica

per il riconoscimento

delle condizioni e per l' arbitraggio del clock e le collisioni sul bus e la

generazione delle corrette temporizzazioni dei segnali.

Osserviamo anche che, pur avendo gli I/O dei PIC una struttura push-pull

(totem pole), i pin configurati per connettersi al bus I2C sono

programmati come open drain, con associato il buffer di ingresso a trigger

di Schmitt.

I moduli integrati nei microcontroller ricalcano questa struttura, ma possono essere

strutturati in modo differente, per cui occorrerà, prima di utilizzarli,

documentarsi sui fogli informativi.

Va considerato che, se il rilevamento delle condizioni di Start e Stop,

ACK e NACK sono eseguite hardware dai moduli di gestione delle

comunicazioni sincrone, la gestione delle operazioni di trasmissione,

delle conseguenze dell' arbitraggio, della gestione multi-master, di

multiplexer o, comunque, delle periferiche, è demandata al software

che controlla il dispositivo.

Quando si comunica con un altro dispositivo I2C, gli 8 bit

di dati possono essere un codice di controllo, un indirizzo o dati grezzi.

Occorrerà verificare i manuali dei vari dispositivi per individuare le

specifiche necessità: diverse periferiche potranno usare codici uguali

con fini differenti e per ognuna si dovrà scrivere la struttura di

controllo e comunicazione adeguata.

In questo senso, I2C può presentare un non indifferente livello di

complicazione, ma, per contro, può dare origine a sistemi complessi

dotati di prestazioni elevate.

|