Caratteristiche specifiche del TIMER0 nelle diverse famiglie di

PIC a 8 bit.

Le differenze di impostazione del Timer0 nei PIC a 8 bit sono minime e questo fa si che una sezione di sorgente

che lo riguarda possa essere portata da un processore all' altro

senza alcuna modifica, in quanto opera in modo eguale su tutti. Questo è un

notevole vantaggio, dato che non è necessario imparare per ogni processore una

diversa gestione del timer.

Esistono comunque piccole differenze che può essere utile conoscere per non

incappare in qualche equivoco che renderebbe problematico l' uso della

periferica.

Utilizzando come base quanto detto fino ad ora riguardo ai Mid-range, vediamo

alcuni particolari per diversi tipi di PIC.

PIC Baseline

Fino ad ora abbiamo usato la struttura dei Mid-range

come esempio.

Per i Baseline vanno considerate due condizioni:

- non è prevista una funzione di interrupt. Pertanto non esiste un registro

INTCON e anche il TIMER0 non genera chiamate interrupt all' overflow (ad

esempio PIC10F2xx)

- l' ingresso di conteggio può essere derivato anche dall' uscita del

comparatore (ad esempio 10F204/206)

Per il resto, i bit di OPTION_REG per il controllo del timer sono identici a

quelli già visti. Anche la struttura è analoga e il prescaler è attribuibile

al TIMER0 o al WDT alternativamente.

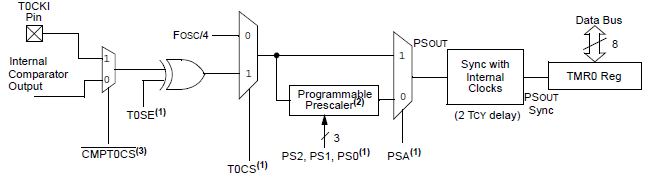

Dunque, nei PIC10F204/206, che dispongono di un comparatore analogico, il

diagramma del TIMER0 è leggermente modificato:

A seconda della sorgente di clock, si possono distinguere tre tipi di

conteggio:

- il primo, analogo a quello disponibili sugli altri PIC, prevede che la

sorgente di conteggio sia derivata dall' oscillatore principale, FOSC/4.

Questa modalità è ottenuta portando a 0 il bit T0CS(OPTION<5>). Il

timer è incrementato ad ogni ciclo di istruzione, se senza prescaler. Se è

selezionato il prescaler, questo dividerà per un fattore fisso gli impulsi

in ingresso.

- il secondo, analogo a quello disponibili sugli altri PIC, fa capo all'

ingresso T0CKI. Questa funzione è scelta portando a 1 il bit

T0CS(OPTION<5>)

Occorre anche settare CMPT0CS(COMCON0<4>) e

COUTEN(COMCON0<6>).

In questo modo il timer incrementa ad ogni transizione sul pin T0CKI

(la

transizione è determinata da T0SE(OPTION<4>). Anche in questo caso il

segnale di conteggio può essere fatto passare attraverso il prescaler.

Il segnale esterno viene sincronizzato con il clock principale e questo

determina un leggero ritardo. Inoltre il segnale esterno di conteggio deve

essere compreso nei limiti previsti dal costruttore. Il foglio dati riporta

i parametri e i diagrammi relativi. La loro consultazione è di una certa

importanza solamente in applicazioni particolarmente critiche per quanto

riguarda la temporizzazione.

- la terza modalità, specifica di questi chip, riguarda la connessione

dell' ingresso di conteggio all' uscita del comparatore. Questo si ottiene

portando a 1 il bit T0CS(OPTION<5>), assieme a

CMPT0CS(COMCON0<4>), mentre COUTEN(COMCON0<6>)

va posto a

0. Ad ogni cambio di stato del comparatore, con il fronte selezionato da T0SE, si avrà un avanzamento del contatore. Anche in questo caso il segnale

di conteggio può essere fatto passare attraverso il prescaler.

| |

T0SE |

CMPT0CS |

COUTEN |

Sorgente conteggio |

| T0CS |

0 |

x |

x |

x |

FOSC/4 |

| 1 |

0 falling

1 rising |

1 |

1 |

ingresso T0CKI |

| 1 |

0 |

uscita comparatore |

Come per gli altri PIC non Enhanced, il prescaler è condiviso con il WDT e

può essere assegnato o a questo o al timer, ma non ad entrambi.

Se è richiesto, durante l' esecuzione del programma, commutare il presclaer

dall' uno all' altro dei due moduli, il foglio dati consiglia la sequenza di

istruzioni adeguata.

Come accennato prima, TIMER0 non genera interrupt all' overflow e questo

richiede una gestione in polling con la rilettura del registro di conteggio TMR0.