PIC Midrange

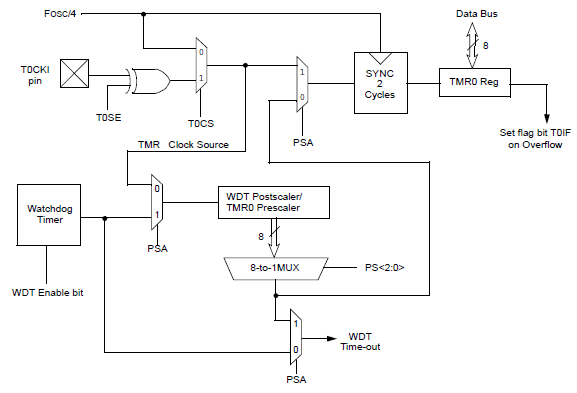

I PIC della famiglia Midrange il TIMER0 ha la struttura finora

vista. Viene mantenuto il registro TMR0 a 8 bit, il prescaler condiviso con

WDT, il clock interno o esterno.

I registri di controllo sono quelli precedentemente visti.

Rispetto ai Baseline i Midrange dispongono di uno stack a 8 livelli e di una

gestione a interrupt, quindi anche TIMER0 è sorgente di interrupt.

La gestione avviene attraverso INTCON (bit T0IE)

e il bit GIE di abilitazione generale.

Il flag T0IF va a 1 al momento

dell' overflow e DEVE essere cancellato da programma, una volta

servito l' interrupt relativo.

Se il flag non viene cancellato, alla riabilitazione di GIE

che fa seguito al retfie,

si generererebbe immediatamente una nuova richiesta di interrupt. |

PIC Midrange Enhanced

I PIC più recenti delle famiglie Base e Mid sono sottoposti ad una

serie di modifiche con lo scopo di migliorarne le prestazioni e facilitarne l'

uso. Ne viene toccato anche il TIMER0. Lo schema tipico per uno di questi processori

è il seguente:

La struttura fondamentale è esattamente la stessa, ovvero c'è la

scelta tra il clock interno e un ingresso esterno T0CKI, la selezione del fronte

di commutazione, il prescaler, i flag di interrupt.

Viene, però, operata una piccola

modifica: il prescaler non è più condiviso con il WDT, ma è dedicato

al timer. Quindi si potrà avere contemporaneamente un prescaler per il TIMER0 e

uno per il WDT. Questo consente una maggiore flessibilità di impiego.

I registri di controllo sono del tutto identici, sia come nome che come

funzioni a livello del singolo bit, anche se può apparire la

denominazione di TMR0CS al posto di T0CS e TMR0SE al posto

di T0SE.

Essendo del tutto identici i bit di controllo, righe scritte per il PIC Baseline,

Mid e Mid Enhanced sono del tutto identiche ed

intercambiabili